# 8Gb (32Mx8Banks×32) Low Power DDR4 SDRAM

### **Descriptions**

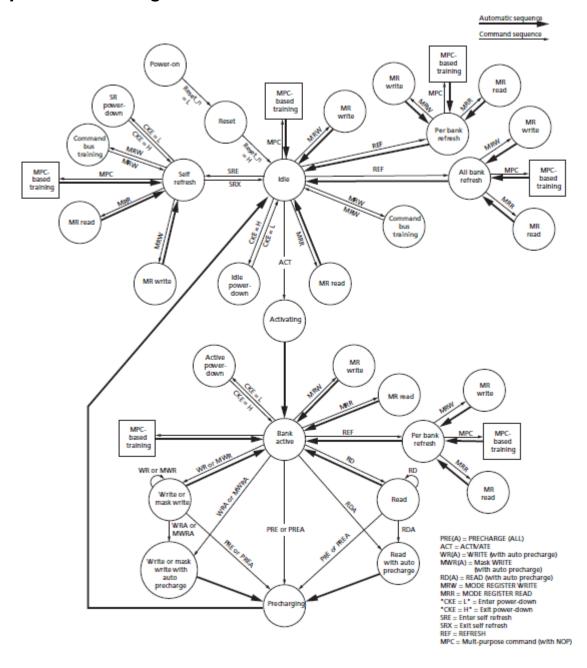

H2AB08G32D6C uses the double data rate architecture on the Command/Address (CA) bus to reduce the number of input pins in the system. Each command uses one clock cycle, during which command information is transferred on both the positive and negative edge of the clock. To achieve high-speed operation, our H2AB08G32D6C • Commands & addresses entered on both positive SDRAM adopt 16n-prefetch interface designed to transfer two data per clock cycle at the I/O pins. A single read or write access for the H2AB08G32D6C effectively consists of a single 8n-bit wide, one clock cycle data transfer at the internal SDRAM core and eight corresponding n-bit wide, one-half-clock-cycle data transfer at the I/O pins. Read and write accesses to the H2AB08G32D6C are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence.

For H2AB08G32D6C devices, accesses begin with the registration of an Active command, which is then followed by a Read or Write command. The address and BA bits registered coincident with the Active command are used to select the row and the Bank to be accessed. The address bits registered coincident with the Read or Write command are used to select the Bank and the starting column location for the burst access.

#### Features

- Bidirectional, data strobe (DQS,/DQS) is transmitted/ received with data, to be used in capturing data at the receiver

- Differential clock inputs (CK and /CK)

- Differential data strobe (DQS and /DQS)

- & negative CK edge; data and data mask referenced to both edges of DQS

- Eight internal banks for concurrent operation

- Data mask (DM) for write data

- Programmable Burst Lengths: 16,32

- Burst type: Sequential or interleave

- Programmable RL (Read latency) & WL (Write latency)

- · Clock Stop capability during idle period

- · Auto Pre-charge for each burst access

- Configurable Drive Strength (DS)

- Auto Refresh and Self Refresh Modes

- Optional Partial Array Self Refresh (PASR) and Temperature Compensated Self Refresh (TCSR)

- Deep Power Down Mode (DPD)

- VDD2/VDDCA/VDDQ= 1.06~1.17V; VDD1= 1.70~1.95V

## **Ordering Information**

| Part No           | Organization | Max. Freq    | Package       | Grade                 |

|-------------------|--------------|--------------|---------------|-----------------------|

| H2AB08G32D6CIAAC  | 256M X 32    | LP DDR4-2400 |               | Commercial (0°~85°)   |

| H2AB08G32D6CKAAC  | 256M X 32    | LP DDR4-3200 | 200Ball       | Commercial (0°~85°)   |

| H2AB08G32D6CIAASL | 256M X 32    | LP DDR4-2400 | BGA,10x14.5mm | Single Low (-30°~85°) |

| H2AB08G32D6CKAASL | 256M X 32    | LP DDR4-3200 |               | Single Low (-30°~85°) |

## Pin Assignment

L

|   | 1                | 2               | 3                | 4                | 5                |

|---|------------------|-----------------|------------------|------------------|------------------|

| Δ | DNU              | DNU             | V <sub>SS</sub>  | V <sub>DD2</sub> | ZQ0              |

| В | DNU              | DQ0_A           | V <sub>DDQ</sub> | DQ7_A            | V <sub>DDQ</sub> |

| c | V <sub>SS</sub>  | DQ1_A           | DMI0_A           | DQ6_A            | V <sub>SS</sub>  |

| D | V <sub>DDQ</sub> | V <sub>SS</sub> | DQS0_t_A         | V <sub>SS</sub>  | V <sub>DDQ</sub> |

| E | V <sub>SS</sub>  | DQ2_A           | DQS0_c_A         | DQ5_A            | V <sub>SS</sub>  |

| F | V <sub>DD1</sub> | DQ3_A           | V <sub>DDQ</sub> | DQ4_A            | V <sub>DD2</sub> |

| G | V <sub>SS</sub>  | ODT_CA_A        | V <sub>SS</sub>  | V <sub>DD1</sub> | V <sub>SS</sub>  |

| Н | V <sub>DD2</sub> | CA0_A           | CS1_A            | CS0_A            | V <sub>DD2</sub> |

| J | V <sub>SS</sub>  | CA1_A           | V <sub>SS</sub>  | CKE0_A           | CKE1_A           |

| K | V <sub>DD2</sub> | V <sub>SS</sub> | V <sub>DD2</sub> | V <sub>SS</sub>  | CS2_A            |

| 8                | 9                | 10               | 11              | 12               |

|------------------|------------------|------------------|-----------------|------------------|

| ZQ1              | V <sub>DD2</sub> | V <sub>SS</sub>  | DNU             | DNU              |

| V <sub>DDQ</sub> | DQ15_A           | V <sub>DDQ</sub> | DQ8_A           | DNU              |

| V <sub>SS</sub>  | DQ14_A           | DMI1_A           | DQ9_A           | V <sub>SS</sub>  |

| V <sub>DDQ</sub> | V <sub>SS</sub>  | DQS1_t_A         | V <sub>SS</sub> | V <sub>DDQ</sub> |

| V <sub>SS</sub>  | DQ13_A           | DQS1_c_A         | DQ10_A          | V <sub>SS</sub>  |

| V <sub>DD2</sub> | DQ12_A           | V <sub>DDQ</sub> | DQ11_A          | V <sub>DD1</sub> |

| V <sub>SS</sub>  | V <sub>DD1</sub> | V <sub>SS</sub>  | ZQ2             | V <sub>SS</sub>  |

| V <sub>DD2</sub> | CA2_A            | CA3_A            | CA4_A           | V <sub>DD2</sub> |

| CK_t_A           | CK_c_A           | V <sub>SS</sub>  | CA5_A           | V <sub>SS</sub>  |

| CKE2_A           | V <sub>SS</sub>  | V <sub>DD2</sub> | V <sub>SS</sub> | V <sub>DD2</sub> |

$\boldsymbol{V_{SS}}$ CS2\_B  $V_{SS}$ Ν CA1\_B  $V_{SS}$  $\mathsf{V}_{\mathsf{SS}}$  $V_{DD2}$ CA0\_B CS1\_B CS0\_B R  $V_{\text{DD2}}$ ODT\_CA\_B  $V_{SS} \\$  $V_{DD1}$  $V_{SS} \\$ DQ3\_B DQ4\_B U  $V_{DD1}$  $V_{DDQ}$  $V_{DD2}$  $V_{SS}$ DQ2\_B DQS0\_c\_B DQ5\_B  $V_{SS}$ W  $V_{DDQ}$  $V_{SS}$  $V_{SS} \\$  $V_{DDQ}$ DQ1\_B DMI0\_B  $\nu_{\text{ss}}$ DQ6\_B  $V_{SS}$ DQ0\_B ДД DNU DQ7\_B  $V_{DDQ}$  $V_{\rm DDQ}$ AB DNU  $V_{SS}$

| CKE2_B           | V                | V                | V               | V                |

|------------------|------------------|------------------|-----------------|------------------|

| CKEZ_B           | V <sub>SS</sub>  | V <sub>DD2</sub> | VSS             | V <sub>DD2</sub> |

| CK_t_B           | CK_c_B           | V <sub>SS</sub>  | CA5_B           | V <sub>SS</sub>  |

| V <sub>DD2</sub> | CA2_B            | CA3_B            | CA4_B           | V <sub>DD2</sub> |

| V <sub>SS</sub>  | V <sub>DD1</sub> | V <sub>SS</sub>  | RESET_n         | V <sub>SS</sub>  |

| V <sub>DD2</sub> | DQ12_B           | V <sub>DDQ</sub> | DQ11_B          | V <sub>DD1</sub> |

| V <sub>SS</sub>  | DQ13_B           | DQS1_c_B         | DQ10_B          | V <sub>SS</sub>  |

| V <sub>DDQ</sub> | V <sub>SS</sub>  | DQS1_t_B         | V <sub>SS</sub> | V <sub>DDQ</sub> |

| V <sub>SS</sub>  | DQ14_B           | DMI1_B           | DQ9_B           | V <sub>SS</sub>  |

| V <sub>DDQ</sub> | DQ15_B           | V <sub>DDQ</sub> | DQ8_B           | DNU              |

| V <sub>SS</sub>  | V <sub>DD2</sub> | V <sub>SS</sub>  | DNU             | DNU              |

| 8                | 9                | 10               | 11              | 12               |

Top View (ball down)

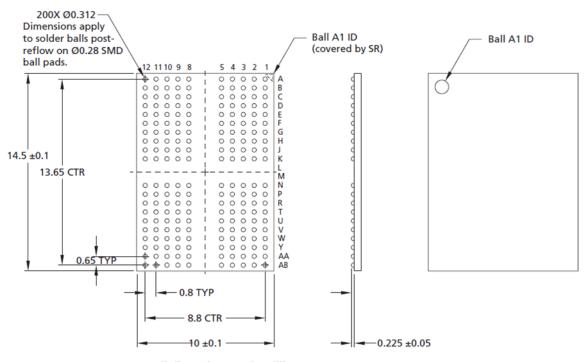

#### 200-Ball FBGA

# Pin Description (Simplified)

| Symbol                                                 | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK_t_A, CK_c_A,<br>CK_t_B, CK_c_B                      | Input     | Clock: CK_t and CK_c are differential clock inputs. All address, command and control input signals are sampled on positive edge of CK_t and the negative edge of CK_c. AC timings for CA parameters are referenced to clock. Each channel (A, B) has its own clock pair.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CKE0_A,<br>CKE1_A,<br>CKE0_B,<br>CKE1_B                | Input     | Clock enable: CKE HIGH activates and CKE LOW deactivates the internal clock signals,input buffers, and output drivers. Power-saving modes are entered and exited via CKE transitions. CKE is sampled at the rising edge of CK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CS0_A, CS1_A,<br>CS0_B,CS1_B                           | Input     | Chip select: Each channel (A, B) has its own CS signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CA[5:0]_A,<br>CA[5:0]_B                                | Input     | Command/address inputs: Provide the command and address inputs according to the command truth table. Each channel (A, B) has its own CA signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ODT_CA_A,<br>ODT_CA_B                                  | Input     | CA ODT Control: The ODT_CA pin is used in conjunction with the mode register to turn on/off the on-die termination for CA pins. It is bonded to VDD2 within the package, or at the package ball, for the terminating rank, and the non-terminating ranks are bonded to VSS (or left floating with a weak pull-down on the DRAM die). The terminating rank is the DRAM that terminates the CA bus for all die on the same channel.                                                                                                                                                                                                                                                                                     |

| DQ[15:0]_A,<br>DQ[15:0]_B                              | I/O       | Data input/output: Bidirectional data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DQS[1:0]_t_A, DQS[1:0]_c_A, DQS[1:0]_t_B, DQS[1:0]_c_B | I/O       | Data strobe: DQS_t and DQS_c are bi-directional differential output clock signals used to strobe data during a READ or WRITE. The data strobe is generated by the DRAM for a READ and is edge-aligned with data. The data strobe is generated by the SoC memory controller for a WRITE and is trained to precede data. Each byte of data has a data strobe signal pair. Each channel (A, B) has its own DQS_t and DQS_c strobes.                                                                                                                                                                                                                                                                                      |

| DMI[1:0]_A,<br>DMI[1:0]_B                              | I/O       | Data Mask/Data Bus Inversion: DMI is a dual use bi-directional signal used to indicate data to be masked, and data which is inverted on the bus. For data bus inversion (DBI), the DMI signal is driven HIGH when the data on the data bus is inverted, or driven LOW when the data is in its normal state. DBI can be disabled via a mode register setting. For data mask, the DMI signal is used in combination with the data lines to indicate data to be masked in a MASK WRITE command (see the Data Mask (DM) and Data Bus Inversion (DBI) sections for details). The data mask function can be disabled via a mode register setting. Each byte of data has a DMI signal. Each channel has its own DMI signals. |

| ZQ0, ZQ1                                               | Reference | ZQ Calibration Reference: Used to calibrate the output drive strength and the termination resistance. There is one ZQ pin per die. The ZQ pin shall be connected to VDDQ through a $240\Omega \pm 1\%$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VDDQ, VDD1,<br>VDD2                                    | Supply    | Power supplies: Isolated on the die for improved noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VSS                                                    | Supply    | Ground Reference: Power supply ground reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RESET_n                                                | Input     | RESET: When asserted LOW, the RESET pin resets both channels of the die.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DNU                                                    |           | Do not use: Must be grounded or left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| NC                                                     |           | No connect: Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

### Absolute Maximum Rating

| Symbol            | ltem                                | Rating     | Units |

|-------------------|-------------------------------------|------------|-------|

| $V_{IN}, V_{OUT}$ | Voltage on any ball relative to VSS | -0.4 ~ 1.5 | V     |

| $V_{DD1}$         | VDD1 supply voltage relative to VSS | -0.4 ~ 2.1 | V     |

| $V_{DD2}$         | VDD2 supply voltage relative to VSS | -0.4 ~ 1.5 | V     |

| $V_{DDQ}$         | VDDQ supply voltage relative to VSS | -0.4 ~ 1.5 | V     |

| T <sub>STG</sub>  | Storage Temperature (plastic)       | -55 ~ 125  | °C    |

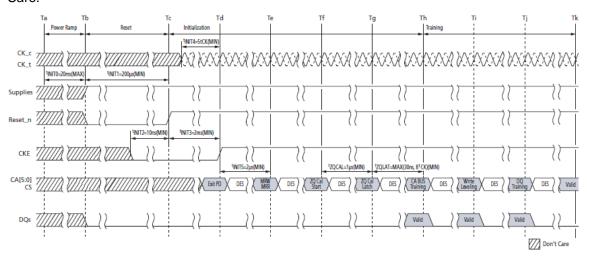

**Note 1:** For information about relationships between power supplies, see the Voltage Ramp and Device Initialization section.

**Note 2:** Storage temperature is the case surface temperature on the center/top side of the device. For measurement conditions, refer to the JESD51-2 standard.

### Input / Output Capacitance

| Symbol            | Parameter                                          | Min. | Max. | Units |

|-------------------|----------------------------------------------------|------|------|-------|

| C <sub>CK</sub>   | Input capacitance, CK_t and CK_c                   | 0.5  | 0.9  | pF    |

| C <sub>DCK</sub>  | Input capacitance delta, CK_t and CK_c             | 0    | 0.09 | pF    |

| Cı                | I Input capacitance, all other input-only pins     | 0.5  | 0.9  | pF    |

| C <sub>DI</sub>   | Input capacitance delta, all other input-only pins | -0.1 | 0.1  | pF    |

| C <sub>IO</sub>   | Input/output capacitance, DQ, DMI, DQS_t, DQS_c    | 0.7  | 1.3  | pF    |

| C <sub>DDQS</sub> | Input/output capacitance delta, DQS_t, DQS_c       | 0    | 0.1  | pF    |

| C <sub>DIO</sub>  | Input/output capacitance delta, DQ, DMI            | -0.1 | 0.1  | pF    |

| $C_{ZQ}$          | Input/output capacitance, ZQ pin                   | 0    | 5.0  | pF    |

Note 1: This parameter is not subject to production testing. It is verified by design and characterization.

Note 2: Absolute value of CKCK\_t - CKCK\_c

Note 3: CI applies to CS, CKE, RESET\_n, and CA[5:0].

**Note 4:** CDI = CI  $-0.5 \times (CCK_t + CKCK_c)$ ; it does not apply to CKE, RESET\_n, or ODT(ca).

Note 5: DMI loading matches DQ and DQS.

Note 6: MR3 I/O configuration for pull-up/pull-down drive strength OP[5:0] = 000000b (RZQ/7).

Note 7: Absolute value of CDQS\_t and CDQS\_c.

**Note 8:** CDIO = CIO  $-0.5 \times (CDQS_t + CDQS_c)$  in byte-lane.

## Recommended DC Operating Conditions

| Symbol    | Parameter             | Min. | Тур. | Max. | Units |

|-----------|-----------------------|------|------|------|-------|

| $V_{DD1}$ | Core Supply voltage 1 | 1.70 | 1.80 | 1.95 | V     |

| $V_{DD2}$ | Core Supply voltage 2 | 1.06 | 1.10 | 1.17 | V     |

| $V_{DDQ}$ | I/O buffer power      | 1.06 | 1.10 | 1.17 | V     |

Notes: 1. VDD1 uses significantly less power than VDD2.

**Notes: 2.** The voltage range is for DC voltage only. DC voltage is the voltage supplied at the DRAM and is inclusive of all noise up to 20 MHz at the DRAM package ball.

**Notes: 3.** The voltage noise tolerance from DC to 20 MHz exceeding a peak-to-peak tolerance of 45mV at the DRAM ball is not included in the TdIVW.

## **DC Characteristics**

(IDD Specifications; VDD2, VDDQ= 1.06~1.17V, VDD1 = 1.70~1.95V)

|        |         | Const. 1.7 ( ) | Speed | 11   |

|--------|---------|----------------|-------|------|

| S      | ymbol   | Supply         | 3200  | Unit |

|        | IDD01   | VDD1           | 7     |      |

| IDD0   | IDD02   | VDD2           | 80    | mA   |

|        | IDD0Q   | VDDQ           | 1.5   |      |

|        | IDD2P1  | VDD1           | 2     |      |

| IDD2P  | IDD2P2  | VDD2           | 3.5   | mA   |

|        | IDD2PQ  | VDDQ           | 1.5   |      |

|        | IDD2PS1 | VDD1           | 2     |      |

| IDD2PS | IDD2PS2 | VDD2           | 3.5   | mA   |

|        | IDD2PSQ | VDDQ           | 1.5   |      |

|        | IDD2N1  | VDD1           | 2     |      |

| IDD2N  | IDD2N2  | VDD2           | 45    | mA   |

|        | IDD2NQ  | VDDQ           | 1.5   |      |

|        | IDD2NS1 | VDD1           | 2     |      |

| IDD2NS | IDD2NS2 | VDD2           | 25    | mA   |

|        | IDD2NSQ | VDDQ           | 1.5   |      |

|        | IDD3P1  | VDD1           | 2     |      |

| IDD3P  | IDD3P2  | VDD2           | 10    | mA   |

|        | IDD3PQ  | VDDQ           | 1.5   |      |

|        | IDD3PS1 | VDD1           | 2     |      |

| DD3PS  | IDD3PS2 | VDD2           | 10    | mA   |

|        | IDD3PSQ | VDDQ           | 1.5   |      |

|        | IDD3N1  | VDD1           | 4     |      |

| IDD3N  | IDD3N2  | VDD2           | 57    | mA   |

|        | IDD3NQ  | VDDQ           | 1.5   |      |

|        | IDD3NS1 | VDD1           | 4     |      |

| IDD3NS | IDD3NS2 | VDD2           | 40    | mA   |

|        | IDD3NSQ | VDDQ           | 1.5   |      |

|        | IDD4R1  | VDD1           | 5     |      |

| IDD4R  | IDD4R2  | VDD2           | 450   | mA   |

|        | IDD4RQ  | VDDQ           | 270   |      |

|        | IDD4W1  | VDD1           | 5     |      |

| IDD4W  | IDD4W2  | VDD2           | 350   | mA   |

|        | IDD4WQ  | VDDQ           | 100   |      |

(IDD Specifications; VDD2, VDDQ= 1.06~1.17V, VDD1 = 1.70~1.95V)

| Symbol |         | Cumply | Speed | l lmi4 |

|--------|---------|--------|-------|--------|

|        |         | Supply | 3200  | Unit   |

|        | IDD51   | VDD1   | 20    |        |

| IDD5   | IDD52   | VDD2   | 170   | mA     |

|        | IDD5Q   | VDDQ   | 1.5   |        |

|        | IDD5AB1 | VDD1   | 4     |        |

| IDD5AB | IDD5AB2 | VDD2   | 60    | mA     |

|        | IDD5ABQ | VDDQ   | 1.5   |        |

|        | IDD5PB1 | VDD1   | 4     |        |

| IDD5PB | IDD5PB2 | VDD2   | 60    | mA     |

|        | IDD5PBQ | VDDQ   | 1.5   |        |

*Notes: 1.* IDD values reflect dual-channel operation with the same pattern for each channel.

**Notes: 2.** Published IDD values except ID4RQ are the maximum of the distribution of the arithmetic mean. Refer to another note for IDD4RQ.

Notes: 1. IDD4RQ value is reference only. Typical value. DBI Disabled, VOH = VDDQ/3, Tc = 25°C

### IDD6 Partial Array Self-refresh current; VDD2, VDDQ = 1.06~1.17V, VDD1 = 1.70~1.95V

| DACD       | Cumply | Ter  | Unit |       |  |

|------------|--------|------|------|-------|--|

| PASR       | Supply | 25°C | 85°C | Offic |  |

| Full Array | VDD1   | 0.4  | 2.2  |       |  |

|            | VDD2   | 0.7  | 7    | mA    |  |

|            | VDDQ   | 0.1  | 1.5  |       |  |

Notes: 1. IDD values reflect dual-channel operation with the same pattern for each channel.

Notes: 2. IDD6 25°C is the typical, and IDD6 85°C is the maximum of the distribution of the arithmetic mean.

# Single-Ended AC and DC Output Levels – ODT Enable

| Voulevel  | Dy Tamainstian (Nam) | VOI  | l lm:t |      |      |

|-----------|----------------------|------|--------|------|------|

| VOH Level | Rx Termination (Nom) | Min. | Тур.   | Max. | Unit |

|           | RZQ/1 (240Ω)         |      |        |      |      |

|           | RZQ/2 (120Ω)         | 0.9  |        |      | VOH  |

| VDDQ/3    | RZQ/3 (80Ω)          |      | 4.0    | 1.1  |      |

| VDDQ/3    | RZQ/4 (60Ω)          |      | 1.0    |      |      |

|           | RZQ/5 (48Ω)          |      |        |      |      |

|           | RZQ/6 (40Ω)          |      |        |      |      |

|           | RZQ/1 (240Ω)         |      |        |      |      |

| VDDQ/2.5  | RZQ/2 (120Ω)         | 0.85 | 1.0    | 1.15 |      |

|           | RZQ/3 (80Ω)          |      |        |      |      |

- **Note 1:** VOH is the calibration comparison point. The output driver calibrates to the VOH level ±10%.

- Note 2: Rx termination values must be set using the MRW command before ZQCal.

- **Note 3:** ZQCal is valid for any Rx termination value given the same VOH level. If the VOH level is changed, ZQCal must be retrained.

### **Differential Output Slew Rate**

| Parameter                                    | Symbol  | Val  | l Init |      |  |

|----------------------------------------------|---------|------|--------|------|--|

| Parameter                                    | Symbol  | Min. | Max.   | Unit |  |

| Differential output slew rate (VOH = VDDQ/3) | SRQdiff | 7    | 18     | V/ns |  |

- Note 1: SR = Slew rate; Q = Query output; se = Differential signal

- Note 2: Measured with output reference load.

- **Note 3:** The output slew rate for falling and rising edges is defined and measured between  $VOL(AC) = 0.2 \times VOH(DC)$  and  $VOH(AC) = 0.8 \times VOH(DC)$ .

- **Note 4:** Slew rates are measured under average SSO conditions with 50% of the DQ signals per data byte switching.

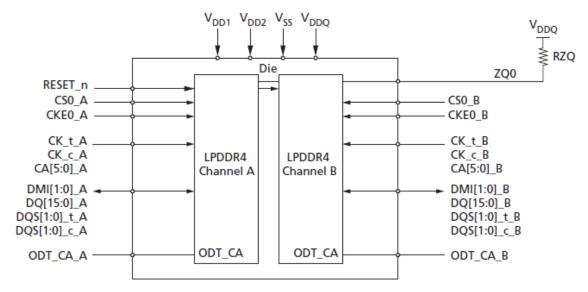

## Block Diagram - Single- Die, Dual-Channel Package

### AC Characteristics

| Cumbal      | Dovementor                                                                           | Min/Max | Data         | Rate | I In:    |

|-------------|--------------------------------------------------------------------------------------|---------|--------------|------|----------|

| Symbol      | Parameter                                                                            | Min/Max | 2400         | 3200 | - Unit   |

| Clock Timir | ng                                                                                   |         |              |      |          |

| .01(/)      | Average clock period                                                                 | Min     | 840          | 625  | ps       |

| tCK(avg)    | Average clock period                                                                 | Max     | 100          | 100  | ns       |

| (CLI/2)     | Average UICH pulse width                                                             | Min     | 0.46         | 0.46 | tCK(avg) |

| tCH(avg)    | Average HIGH pulse width                                                             | Max     | 0.54         | 0.54 | tCK(avg) |

| (CL (a) (a) | Average LOW pulse width                                                              | Min     | 0.46         | 0.46 | tCK(avg) |

| tCL(avg)    | Average LOW pulse width                                                              | Max     | 0.54         | 0.54 | tCK(avg) |

| tCK(abs)    | Absolute clock period                                                                | Min     | tCK(avg) MIN | ps   |          |

| (CLI/aha)   | Absolute clock HICH pulse width                                                      | Min     | 0.43         | 0.43 | tCK(avg) |

| tCH(abs)    | Absolute clock HIGH pulse width                                                      | Max     | 0.57         | 0.57 | tCK(avg) |

| .01 (-1)    | Absolute alsold I OW mules width                                                     | Min     | 0.43         | 0.43 | tCK(avg) |

| tCL(abs)    | Absolute clock LOW pulse width                                                       | Max     | 0.57         | 0.57 | tCK(avg) |

| tJIT(per),  | Clark paried litter                                                                  | Min     | -            | -40  | ps       |

| allowed     | Clock period jitter                                                                  | Max     | -            | 40   | ps       |

| tJIT(cc),   | Maximum clock jitter between two consecutive clock cycles (with clock period jitter) | Max     | -            | 80   | ps       |

| Symbol               | Parameter                                                      | Min/ | Data                                        | Rate             | Unit     |  |  |

|----------------------|----------------------------------------------------------------|------|---------------------------------------------|------------------|----------|--|--|

| Symbol               | Parameter                                                      | Max  | 2400                                        | 3200             | Unit     |  |  |

| ZQ Calibrati         | on Parameters                                                  |      |                                             |                  |          |  |  |

| tZQCAL               | ZQCAL START to ZQCAL LATCH command interval                    | Min  | 1                                           |                  | us       |  |  |

| tZQLAT               | ZQCAL LATCH to next valid command interval                     | Min  | MAX(30n                                     | s, 8nCK)         | ns       |  |  |

| tZQRESET             | ZQCAL RESET to next valid command interval Min MAX(50ns, 3nCK) |      |                                             |                  |          |  |  |

| <b>READ Parar</b>    | neters                                                         |      |                                             |                  |          |  |  |

| 1000014              | DOCtrust time from OV                                          | Min  | 150                                         | 00               | ps       |  |  |

| tDQSCK               | DQS output access time from CK                                 | Max  | 350                                         | 00               | ps       |  |  |

| tDQSCK_<br>VOLT      | DQS output access time from CK_t/CK_c – voltage variation      | Max  | 7                                           |                  | ps/mV    |  |  |

| tDQSCK_<br>TEMP      | DQS output access time from CK_t/CK_c – temperature variation  | Max  | 4                                           |                  | ps°/C    |  |  |

| tDQSCK_r<br>ank2rank | CK to DQS rank to rank variation                               | Max  | 1.                                          | ns               |          |  |  |

| tDQSQ                | DQS-DQ skew                                                    | Max  | 0.1                                         | UI               |          |  |  |

| tQH                  | DQ output hold time total from DQS_t, DQS_c                    | Min  | Min (tQS                                    | ps               |          |  |  |

| tRPRE                | READ preamble                                                  | Min  | 1.                                          | tCK(avg)         |          |  |  |

| tRPST                | READ postamble                                                 | Min  | 0.                                          | 4                | tCK(avg) |  |  |

| tLZ(DQS)             | DQS Low-Z from clock                                           | Min  | (RL x tCK) + tDQSCK<br>x tCK) -             |                  | ps       |  |  |

| tLZ(DQ)              | DQ Low-Z from clock                                            | Min  | (RL x tCK) + tDQS                           | SCK(Min) - 200ps | ps       |  |  |

| tHZ(DQS)             | DQS High-Z from clock                                          | Min  | (RL x tCK) + tDQSCK(<br>(tRPST(Max) x       | , , ,            | ps       |  |  |

| tHZ(DQ)              | DQ High-Z from clock                                           | Max  | $t(RL \times tCK) + tD$<br>tDQSQ(Max) + (BL | , ,              | ps       |  |  |

| tQW_total            | Data output valid window time total, per pin                   | Min  | 0.73                                        | 0.68             | UI       |  |  |

| tDQSQ_DBI            | DQS_t, DQS_c to DQ skew total, per group, per access           | Max  | 0.1                                         | 18               | UI       |  |  |

| tQH_DBI              | DQ output hold time total from DQS_t, DQS_c                    | Min  | MIN(tQSH_DE                                 | BI, tQSL_DBI)    | ps       |  |  |

| tQW_total_DBI        | Data output valid window time total, per pin                   | Min  | 0.73                                        | 0.68             | UI       |  |  |

| tQSL                 | DQS_t, DQS_c differential output LOW time                      | Min  | tCL(abs)                                    | ) - 0.05         | tCK(avg) |  |  |

| tQSH                 | DQS_t, DQS_c differential output HIGH time                     | Min  | tCH(abs                                     | ) – 0.05         | tCK(avg) |  |  |

| tworr                | · ·                                                            |      | •                                           |                  |          |  |  |

| tQSL-DBI             | DQS_t, DQS_c differential output LOW time                      | Min  | tCL(abs)                                    | -0.045           | tCK(avg) |  |  |

| Symbol      | Parameter                                     | Min/   | Data             | Rate        | Unit    |  |

|-------------|-----------------------------------------------|--------|------------------|-------------|---------|--|

| Symbol      | Parameter                                     | Max    | 2400             | 3200        | Unit    |  |

| CKE Input F | Parameters                                    |        |                  |             |         |  |

| tCKE        | CKE minimum pulse width(HIGH and LOW          | Min    | May/7 5r         | ns, 4nCK)   | ns      |  |

| IONE        | pulse width)                                  | IVIIII | IVIAX(1.51       | 15, 41101() | 113     |  |

| tCMDCKE     | Delay from valid command to CKE input         | Min    | Max(1.75         | ns          |         |  |

|             | LOW                                           |        |                  |             |         |  |

| tCKELCK     | Valid clock requirement after CKE input       | Min    | MAX(5n           | s, 5nCK)    | ns      |  |

|             | LOW                                           |        |                  |             |         |  |

| tCSCKE      | Valid CS requirement before CKE input LOW     | Min    |                  | 75          | ns      |  |

| tCKELCS     | Valid CS requirement after CKE input LOW      | Min    | MAX(5n           | s, 5nCK)    | ns      |  |

| tCKCKEH     | Valid Clock requirement before CKE Input HIGH | Min    | MAX(1.75         | ns, 3nCK)   | ns      |  |

| tXP         | Exit power-down to next valid command         | Min    | MAY/7 5,         | ns, 5nCK)   | nc      |  |

| WE          | delay                                         | IVIIII | IVIAA(7.5I       | 15, 5HCK)   | ns      |  |

| tCSCKEH     | Valid CS requirement before CKE input HIGH    | Min    | 1.               | ns          |         |  |

| tCKEHCS     | Valid CS requirement after CKE input HIGH     | Min    | MAX(7.5r         | ns, 5nCK)   | ns      |  |

|             | Valid clock and CS requirement after CKE      | D 41 - | NAAN//4 A .      |             |         |  |

| tMRWCKEL    | input LOW after MRW command                   | Min    | MAX(14n          | s, 10nCK)   | ns      |  |

|             | Valid clock and CS requirement after CKE      |        |                  |             |         |  |

| tZQCKE      | input LOW after ZQ calibration start          | Min    | MAX(1.75         | ns, 3nCK)   | ns      |  |

|             | command                                       |        |                  |             |         |  |

| Command A   | Address Input Parameters                      |        |                  |             |         |  |

| tcIVW       | Command/address valid window                  | Min    | 0                | .3          | tCK(avg |  |

| tcIPW       | Address and control input pulse width         | Min    | 0                | tCK(avg     |         |  |

| Boot Param  | eters (10–55 MHz)                             |        |                  |             |         |  |

| 014         | Clask avalations                              | Max    | 10               | 00          | ns      |  |

| tCKb        | Clock cycle time                              | Min    | 1                | 8           | ns      |  |

| -DOGGKI-    | DOS autout data aggest time from CV           | Min    | ,                | 1           | ns      |  |

| tDQSCKb     | DQS output data access time from CK           | Max    | 1                | 0           | ns      |  |

| tDQSQb      | Data strobe edge to output data edge          | Max    | 1                | .2          | ns      |  |

| Mode Regis  | ter Parameters                                |        |                  |             |         |  |

| tMRW        | MODE REGISTER WRITE command period            | Min    | MAX(10n          | s, 10nCK)   | ns      |  |

| tMRR        | MODE REGISTER READ command period             | Min    | 8                | 3           | tCK(avg |  |

| tMRRI       | Additional time after tXP has expired until   | Min    | tDCD/mir         | 2) + 35℃K   | no      |  |

| TIVINNI     | MRR command may be issued                     | IVIIII | tRCD(min) + 3nCK |             | ns      |  |

| tSDO        | Delay from MRW command to DQS driven          | Max    | MAV/125          | CK 20nc)    | nc      |  |

| ISDO        | out                                           | IVIAX  | MAX(12nCK, 20ns) |             | ns      |  |

$(V_{DD2,}\ V_{DDQ,}\ V_{DDCA}\!=\!1.06{\sim}1.17V,\ V_{DD1}=\!1.70{\sim}1.95V)$

| Cumbal     | Parameter                                     | Min/Max   | Data                    | Rate                                           | Unit     |

|------------|-----------------------------------------------|-----------|-------------------------|------------------------------------------------|----------|

| Symbol     | Parameter                                     | WIIII/Wax | 2400                    | 3200                                           | Unit     |

| Core Parar | neters                                        |           |                         |                                                |          |

| RL-A       | READ latency (DBI disabled)                   | Min       | 22 28                   |                                                | tCK(avg) |

| RL-B       | READ latency (DBI enabled))                   | Min       | 25                      | 32                                             | tCK(avg) |

| WL-A       | WRITE latency (Set A)                         | Min       | 11                      | 14                                             | tCK(avg) |

| WL-B       | WRITE latency (Set B)                         | Min       | 20                      | 26                                             | tCK(avg) |

| tRC        | ACTIVATE-to-ACTIVATE command period           | Min       | (with all-ban<br>tRAS + | tRPab<br>k precharge)<br>tRPpb<br>nk precharge | ns       |

| tSR        | Minimum self refresh time (entry to exit)     | Min       | MAX(15r                 | ns                                             |          |

| tXSR       | Self refresh exit to next valid command delay | Min       | MAX(tRFC                | ns                                             |          |

| tCCD       | CAS-to-CAS delay                              | Min       | 3                       | tCK(avg)                                       |          |

| tCCDMW     | CAS-to-CAS delay masked write                 | Min       | Min 32                  |                                                |          |

| tRTP       | Internal READ to PRECHARGE command delay      | Min       | Max (7.5ns, 8nCK)       |                                                | ns       |

| tRCD       | RAS-to-CAS delay                              | Min       | Max (18r                | ns, 4nCK)                                      | ns       |

| tRPpb      | Row precharge time (single bank)              | Min       | Max (18r                | ns, 3nCK)                                      | ns       |

| tRPpab     | Row precharge time (all banks)                | Min       | Max (21r                | ns                                             |          |

|            |                                               | Min       | Max (42r                | ns, 3nCK)                                      | ns       |

| tRAS       | Row active time                               | Max       | `                       | FI × Refresh<br>, 70.2)                        | us       |

| tWR        | WRITE recovery time                           | Min       | Max (18r                | ns, 4nCK)                                      | ns       |

| tWTR       | WRITE-to- READ command delay                  | Min       | Max (10r                | ns, 8nCK)                                      | ns       |

| tRRD       | Active bank A to active bank B                | Min       | Max (10r                | ns, 4nCK)                                      | ns       |

| tPPD       | Precharge-to-precharge delay                  | Min       | 4                       | tCK(avg)                                       |          |

| tFAW       | Four-bank activate window                     | Min       | 4                       | ns                                             |          |

| tESCKE     | Delay from SRE command to CKE input LOW       | Min       | MAX(1.75                | ns, 3nCK)                                      | -        |

| Cumbal             | Darameter                                                   | Min/May | Data I    | Rate   | I Init |

|--------------------|-------------------------------------------------------------|---------|-----------|--------|--------|

| Symbol             | Parameter                                                   | Min/Max | 2400      | 3200   | Unit   |

| <b>CA Training</b> | Parameters                                                  |         |           |        |        |

| tCKELCK            | Valid clock requirement after CKE Input LOW                 | Min     | MAX(5ns   | tCK    |        |

| tDStrain           | Data setup for VREF training mode                           | Min     | 2         |        | ns     |

| tDHtrain           | Data hold for VREF training mode                            | Min     | 2         |        | ns     |

| tADR               | Asynchronous data read y                                    | Max     | 20        | )      | ns     |

| tCACD              | CA BUS TRAINING command-<br>to-command delay                | Min     | RU(tAD    | R/tCK) | tCK    |

| tDQSCKE            | Valid strobe requirement before CKE LOW                     | Max     | 10        | )      | ns     |

| tCAENT             | First CA BUS TRAINING command following CKE LOW             | Min     | 25        | ns     |        |

| tVREFca_LO<br>NG   | VREF step time – multiple steps                             | Max     | 25        | ns     |        |

| tVREFca_S<br>HORT  | VREF step time – one step                                   | Max     | 80        | ns     |        |

| tCKPRECS           | Valid clock requirement before CS<br>HIGH                   | Min     | 2tCK -    | -      |        |

| tCKPSTCS           | Valid clock requirement after CS HIGH                       | Min     | MAX(7.5n  | -      |        |

| tCS_VREF           | Minimum delay from CS to DQS toggle in command bus training | Min     | 2         | tCK    |        |

| tCKEHDQS           | Minimum delay from CKE HIGH to strobe High-Z                | Min     | 10        | )      | ns     |

| tMRZ               | CA bus training CKE HIGH to DQ tri-state                    | Min     | 1.5       | 5      | ns     |

| tCKELODTo<br>n     | ODT turn-on latency from CKE                                | Min     | 20        | )      | ns     |

| tCKEHODTo<br>ff    | ODT turn-off latency from CKE                               | Min     | 20        | ns     |        |

| Write Voltag       | je and Timing                                               |         |           |        | -      |

| TdIVW_total        | Rx timing window total at VdIVW voltage levels              | Max     | 0.22 0.25 |        | UI     |

| TdIVW_1-bit        | Rx timing window 1-bit toggle (at VdIVW voltage levels)     | Max     | ТВ        | UI     |        |

# H2AB08G32D6C

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 112/10000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DQ and DMI input pulse width (at VCENT_DQ)               | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | UI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| DO . DOO                                                 | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| DQ-to-DQS offset                                         | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 800                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | - ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| DQ-to-DQ offset                                          | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| DQ-to-DQS offset temperature variation                   | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ps/°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| DQ-to-DQS offset voltage variation                       | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ps/50mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| WRITE command to first DOS transition                    | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | tCK(ova)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| WRITE command to first DQS transition                    | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | tCK(avg)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| DQS input HIGH-level width                               | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | tCK(avg)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| DQS input LOW-level width                                | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | tCK(avg)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| DQS falling edge to CK setup time                        | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | tCK(avg)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |