# 16G-Bit 3.3V NAND FLASH MEMORY

### Descriptions

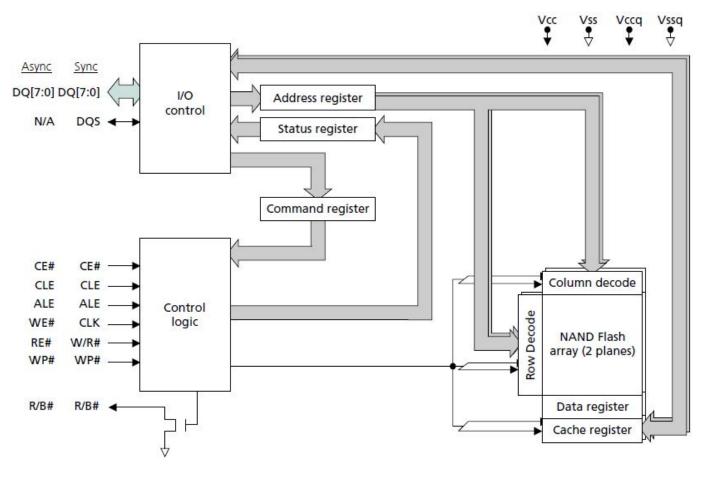

The H7A2AG21C1CX (16G-bit) NAND Flash devices include an asynchronous data interface for high-performance I/O operations. These devices use a highly multiplexed 8-bit bus (DQx) to transfer commands, address, and data. There are five control signals used to implement the asynchronous data interface: CE#, CLE, ALE, WE#, and RE#. Additional signals control hardware write protection (WP#) and monitor device status (R/B#).

The H7A2AG21C1CX (16G-bit) NAND Flash device additionally includes a synchronous data interface for high-performance I/O operations. When the synchronous interface is active, WE# becomes CLK and RE# becomes W/R#. Data transfers include a bidirectional data strobe (DQS).

This hardware interface creates a low pin-count device with a standard pinout that remains the same from one density to another, enabling future upgrades to higher densities with no board redesign.

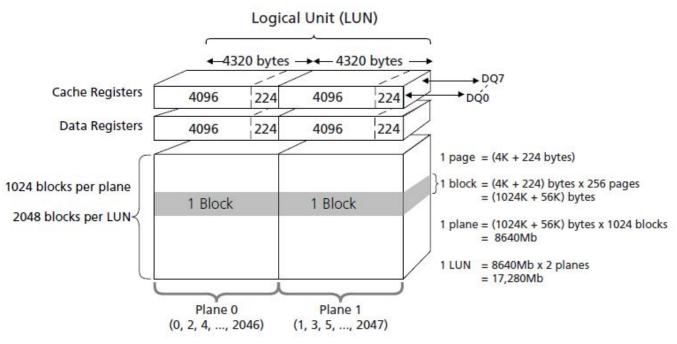

A target is the unit of memory accessed by a chip enable signal. A target contains one or more NAND Flash die. A NAND Flash die is the minimum unit that can independently execute commands and report status. A NAND Flash die, in the ONFI specification, is referred to as a logical unit (LUN).

### Features

- Open NAND Flash Interface (ONFI) 2.2-compliant1

- Multiple-level cell (MLC) technology

- Organization

- Page size x8: 4320 bytes (4096 + 224 bytes)

- Block size: 256 pages (1024K + 56K bytes)

- Plane size: 2 planes x 1024 blocks per plane

- Device size: 16Gb: 2048 blocks;32Gb: 4096 blocks

- Synchronous I/O performance

- Up to synchronous timing mode 4

- Clock rate: 12ns (DDR)

- Read/write throughput per pin: 166 MT/s

- Asynchronous I/O performance

- Up to asynchronous timing mode 5

- Read/write throughput per pin: 50 MT/s

- tRC/tWC: 20ns (MIN)

- Array performance

- Read page: 75  $\mu$  s (MAX)

- Program page: 1300  $\mu$  s (TYP)

- Erase block: 3.8ms (TYP)

- Operating Voltage Range

- VCC: 2.7 3.6V

- VCCQ: 2.7 3.6V

- Command set: ONFI NAND Flash Protocol

- Advanced Command Set

- Program cache

- Read cache sequential

- Read cache random

- One-time programmable (OTP) mode

- Multi-plane commands

- Multi-LUN operations

- Read unique ID

- Copyback

- Operating temperature:

- Commercial: 0°C to +70°C

- Package: 48-pin TSOP

#### **Ordering Information**

| Part No      | Density            | Organization | Package                 | Grade      |

|--------------|--------------------|--------------|-------------------------|------------|

| H7A2AG21C1CX | 16G-bit/2048M-byte | X8           | 48-Pin<br>TSOP1 12x20mm | Commercial |

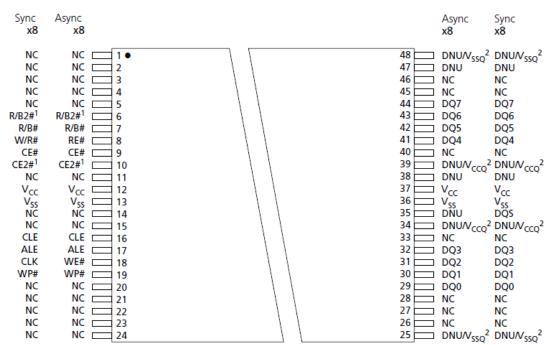

### Pin Assignment

- Notes: 1. CE2# and R/B2# are available on dual die packages. They are NC for other configurations.

- 2. These V<sub>CCQ</sub> and V<sub>SSQ</sub> pins are for compatibility with ONFI 2.2. If not supplying V<sub>CCQ</sub> or V<sub>SSQ</sub> to these pins, do not use them.

### Pin Description (Simplified)

|                 | 48-pin TSOP1,12x20mm |                            |  |  |  |  |  |

|-----------------|----------------------|----------------------------|--|--|--|--|--|

| Pin Name        | I/O                  | Function                   |  |  |  |  |  |

| #WP             | Input                | Write Protect              |  |  |  |  |  |

| ALE             | Input                | Address Latch Enable       |  |  |  |  |  |

| #CE             | Input                | Chip Enable                |  |  |  |  |  |

| #WE             | Input                | Write Enable and clock     |  |  |  |  |  |

| R/B#            | Output               | Ready/Busy                 |  |  |  |  |  |

| #RE             | Input                | Read Enable and write/read |  |  |  |  |  |

| CLE             | Input                | Command Latch Enable       |  |  |  |  |  |

| DQX             | Input / Output       | Data Input / Output (x8)   |  |  |  |  |  |

| V <sub>cc</sub> | Supply               | Power Supply               |  |  |  |  |  |

| V <sub>SS</sub> | Supply               | Ground                     |  |  |  |  |  |

| DNU             | -                    | Do Not Use:                |  |  |  |  |  |

| N.C             | -                    | Not Connect                |  |  |  |  |  |

Note1: Connect all Vcc and Vss pins to power supply or ground. Do not leave Vcc or Vss disconnected.

### Absolute Maximum Rating(3.3V)

| ltem                         | Symbol           | Conditions         | Rating     | Unit |

|------------------------------|------------------|--------------------|------------|------|

| Supply Voltage               | V <sub>cc</sub>  |                    | -0.6 ~ 4.6 | V    |

| Voltage Applied to Any Pin   | V <sub>in</sub>  | Relative to Ground | -0.6 ~ 4.6 | V    |

| Storage Temperature          | T <sub>STG</sub> |                    | -65 ~ 150  | °C   |

| Short circuit output current | l <sub>os</sub>  |                    | 5          | mA   |

**Note 1:** Minimum DC voltage is -0.6V on input/output pins. During transitions, this level may undershoot to -2.0V for periods <30ns.

*Note 2:* Maximum DC voltage on input/output pins is Vcc+0.3V which, during transitions, may overshoot to Vcc+2.0V for periods <20ns.

*Note 3:* This device has been designed and tested for the specified operation ranges. Proper operation outside of these levels is not guaranteed. Exposure to absolute maximum ratings may affect device reliability. Exposure beyond absolute maximum ratings may cause permanent damage.

### **Operating Ranges(3.3V)**

| Parameter                      | Symbol | Conditions | Spe  | Unit |      |  |

|--------------------------------|--------|------------|------|------|------|--|

| Falameter                      | Symbol | Conditions | Min. | Max. | Unit |  |

| Supply Voltage                 | Vcc    |            | 2.7  | 3.6  | V    |  |

| Ambient Temperature, Operating | Та     | Commercial | 0    | 70   | °C   |  |

### DC Characteristics(Asynchronous)

| Devementere                                             | Cumple of | Conditions                          |     | Spec. |     | 11   |

|---------------------------------------------------------|-----------|-------------------------------------|-----|-------|-----|------|

| Parameters                                              | Symbol    | Conditions                          | MIN | ТҮР   | Max | Unit |

| Array read current<br>(active)                          | lcc1      | -                                   | -   | 20    | 50  | mA   |

| Array program current<br>(active)                       | lcc2      | -                                   | -   | 20    | 50  | mA   |

| Erase current (active)                                  | lcc3      | -                                   | -   | 20    | 50  | mA   |

| I/O burst read current                                  | Icc4R     | tRC = tRC (MIN); IOUT=<br>0mA       | -   | 8     | 10  | mA   |

| I/O burst write current                                 | Icc4W     | tWC = tWC (MIN)                     | -   | 8     | 10  | mA   |

| Bus idle current                                        | lcc5      | -                                   | -   | 3     | 5   | mA   |

| Current during first<br>RESET<br>command after power-on | lcc6      | -                                   | -   | -     | 10  | mA   |

| Standby current - VCC                                   | ISB       | CE# = VCCQ - 0.2V;<br>WP# = 0V/VCCQ | -   | 10    | 50  | uA   |

| Standby current - VCCQ                                  | ISBQ      | CE# = VCCQ - 0.2V;<br>WP# = 0V/VCCQ | -   | 3     | 10  | uA   |

| Staggered power-up<br>current                           | IST       | tRISE = 1ms; CLINE =<br>0.1uF       | -   | -     | 10  | mA   |

### DC Characteristics(Synchronous)

| Devementare                          | Cumhal | Conditions                          |     | Spec. |     | 11:0:1 |

|--------------------------------------|--------|-------------------------------------|-----|-------|-----|--------|

| Parameters                           | Symbol | Conditions                          | MIN | TYP   | Max | Unit   |

| Array read current<br>(active)       | lcc1   | CE# = VIL; tCK = tCK<br>(MIN)       | -   | 25    | 50  | mA     |

| Array program current<br>(ac-active) | lcc2   | tCK = tCK (MIN)                     | -   | 25    | 50  | mA     |

| Erase current (active)               | lcc3   | tCK = tCK (MIN)                     | -   | 25    | 50  | mA     |

| I/O burst read current               | Icc4R  | tCK = tCK (MIN)                     | -   | 20    | 27  | mA     |

| I/O burst write current              | Icc4W  | tCK = tCK (MIN)                     | -   | 20    | 27  | mA     |

| Bus idle current                     | lcc5   | tCK = tCK (MIN)                     | -   | 5     | 10  | mA     |

| Standby current - VCC                | ISB    | CE# = VCCQ - 0.2V;<br>WP# = 0V/VCCQ | -   | 10    | 50  | uA     |

| Standby current - VCCQ               | ISBQ   | CE# = VCCQ - 0.2V;<br>WP# = 0V/VCCQ | -   | 3     | 10  | uA     |

### DC Characteristics(VCCQ)

| Parameters                   | Symphol    | Conditiono                                                           |     | Spec. |       | 110:4 |

|------------------------------|------------|----------------------------------------------------------------------|-----|-------|-------|-------|

| Parameters                   | Symbol     | Conditions                                                           | MIN | ТҮР   | Max   | Unit  |

| AC input high voltage        | VIH(AC)    | CE#, DQ[7:0], DQS,                                                   | -   | 25    | 35    | mA    |

| AC input low voltage         | VIL(AC)    | ALE, CLE, CLK<br>(WE#), W/R# (RE#),<br>WP#                           | -   | 25    | 35    | mA    |

| DC input high voltage        | VIH(DC)    | DQ[7:0], DQS, ALE,                                                   | -   | 25    | 35    | mA    |

| DC input low voltage         | VIL(DC)    | CLE, CLK<br>(WE#), W/R# (RE#)                                        | -   | -     | 1     | mA    |

| Input leakage current        | ILI        | Any input VIN = 0V to<br>VCCQ<br>(all other pins under test<br>= 0V) | -   | 20    | 100   | uA    |

| Output leakage current       | ILO        | DQ are disabled; VOUT<br>= 0V to<br>VCCQ                             | -   | -     | +/-10 | uA    |

| Output low current<br>(R/B#) | IOL (R/B#) | VOL = 0.4V                                                           | -   | -     | +/-10 | uA    |

**Notes 1:** All leakage currents are per die (LUN). Two die (LUNs) have a maximum leakage current of ±20µA and four die (LUNs) have a maximum leakage current of ±40µA in the asynchronous interface.

*Notes 2:* DC characteristics may need to be relaxed if R/B# pull-down strength is not set to full strength.

### AC Measurement Conditions(3.3V)

| Devemeter                          | Symbol | Spec.              | l Init |            |

|------------------------------------|--------|--------------------|--------|------------|

| Parameter                          | Symbol | Device             | Мах    | Unit       |

| Input capacitance – ALE, CE#, CLE, | CINI   | Single die package | 6      |            |

| RE#, WE#, WP#                      | CIN    | Dual die package   | 10     | - <b>F</b> |

| Input/output capacitance –         | 010    | Single die package | 5      | pF         |

| DQ[7:0], DQS                       | CIO    | Dual die package   | 8      |            |

*Note :* These parameters are verified in device characterization and are not 100% tested. Test conditions: TC =  $25^{\circ}$ C; f = 1 MHz; Vin = 0V.

# AC timing characteristics for Command, Address and Data Input(3.3V)

| Deremeter                | Cumhal | Sp  | Spec. |      |  |

|--------------------------|--------|-----|-------|------|--|

| Parameter                | Symbol | MIN | MAX   | Unit |  |

| ALE to Data Loading Time | tADL   | 70  | -     | ns   |  |

| ALE Hold Time            | tALH   | 5   | -     | ns   |  |

| ALE setup Time           | tALS   | 10  | -     | ns   |  |

| #CE Hold Time            | tCH    | 5   | -     | ns   |  |

| CLE Hold Time            | tCLH   | 5   | -     | ns   |  |

| CLE setup Time           | tCLS   | 10  | -     | ns   |  |

| #CE setup Time           | tCS    | 15  | -     | ns   |  |

| Data Hold Time           | tDH    | 5   | -     | ns   |  |

| Data setup Time          | tDS    | 7   | -     | ns   |  |

| Write Cycle Time         | tWC    | 20  | -     | ns   |  |

| #WE High Hold Time       | tWH    | 7   | -     | ns   |  |

| #WE Pulse Width          | tWP    | 10  | -     | ns   |  |

| #WP setup Time           | tWW    | 100 | -     | ns   |  |

*Note: 1.* tADL is the time from the #WE rising edge of final address cycle to the #WE rising edge of first data cycle.

### AC timing characteristics for Operation(3.3V)

| Beremeter                          | Cymrhal | Sp  | ec.      | 11   |

|------------------------------------|---------|-----|----------|------|

| Parameter                          | Symbol  | MIN | MAX      | Unit |

| ALE to #RE Delay                   | tAR     | 10  | -        | ns   |

| #CE Access Time                    | tCEA    | -   | 25       | ns   |

| #CE HIGH to Output High-Z(1)       | tCHZ    | -   | 30       | ns   |

| CLE to #RE Delay                   | tCLR    | 10  | -        | ns   |

| #CE HIGH to Output Hold            | tCOH    | 15  | -        | ns   |

| Cache read busy time               | tRCBSY  | 3   | 75       | us   |

| Output High-Z to #RE LOW           | tIR     | 0   | -        | ns   |

| READ PAGE operation time           | tR      | -   | 75       | us   |

| READ Cycle Time                    | tRC     | 20  | -        | ns   |

| #RE Access Time                    | tREA    | -   | 16       | ns   |

| #RE HIGH Hold Time                 | tREH    | 7   | -        | ns   |

| #RE HIGH to Output Hold            | tRHOH   | 15  | -        | ns   |

| #RE HIGH to #WE LOW                | tRHW    | 100 | -        | ns   |

| #RE HIGH to Output High-Z(1)       | tRHZ    | -   | 200      | ns   |

| #RE LOW to output hold             | tRLOH   | 0   | -        | ns   |

| #RE Pulse Width                    | tRP     | 10  | -        | ns   |

| Ready to #RE LOW                   | tRR     | 20  | -        | ns   |

| Reset Time (READ/PROGRAM/ERASE)(2) | tRST    | -   | 5/10/500 | us   |

| #WE HIGH to Busy(3)                | tWB     | -   | 200      | ns   |

| #WE HIGH to #RE LOW                | WHR     | 60  | -        | ns   |

*Note 1:* Transition is measured ±200mV from steady-state voltage with load. This parameter is sampled and not 100 % tested

*Note 2:* Do not issue new command during tWB, even if RY/#BY is ready.

### **Program and Erase Characteristics**

| Denemater                                                      | Ourseland | Sp   | ec.  | l Init |

|----------------------------------------------------------------|-----------|------|------|--------|

| Parameter                                                      | Symbol    | TYP  | MAX  | Unit   |

| Number of partial page programs                                | NoP       | -    | 1    | cycles |

| Page Program time                                              | tPROG     | 1300 | 2600 | us     |

| Busy Time for Cache program (1)                                | tCBSY     | -    | 40   | us     |

| Busy Time for SET FEATURES /GET FEATURES                       | tFEAT     | -    | 1    | us     |

| Busy Time for program/erase at locked block                    | tLBSY     | -    | 3    | us     |

| Busy Time for OTP program when OTP is protected                | tOBSY     | -    | 40   | us     |

| Block Erase Time                                               | tBERS     | 3.8  | 10   | ms     |

| Last Page Program time (2)                                     | tLPROG    | -    | -    | -      |

| Busy Time for Two Plane page program and Two Plane Block Erase | tDBSY     | 0.5  | 1    | us     |

**Note: 1.** tCBSY maximum time depends on timing between internal program complete and data-in.

Note: 2. tLPROG = Last tPROG + Last -1 tPROG – Last page Address, Command and Data load time.

# H7A2AG21C1CX

### Block Diagram

### Memory Array Organization

| Cycle  | DQ7  | DQ6  | DQ5  | DQ4               | DQ3              | DQ2  | DQ1  | DQ0              |

|--------|------|------|------|-------------------|------------------|------|------|------------------|

| First  | CA7  | CA6  | CA5  | CA4               | CA3              | CA2  | CA1  | CA0 <sup>2</sup> |

| Second | LOW  | LOW  | LOW  | CA12 <sup>3</sup> | CA11             | CA10 | CA9  | CA8              |

| Third  | PA7  | PA6  | PA5  | PA4               | PA3              | PA2  | PA1  | PA0              |

| Fourth | BA15 | BA14 | BA13 | BA12              | BA11             | BA10 | BA9  | BA8 <sup>4</sup> |

| Fifth  | LOW  | LOW  | LOW  | LOW               | LA0 <sup>5</sup> | BA18 | BA17 | BA16             |

#### Table 2: Array Addressing for Logical Unit (LUN)

*Notes: 1.* CAx = column address, PAx = page address, BAx = block address, LAx = LUN address; the page address, block address, and LUN address are collectively called the row address.

*Notes: 3.* Column addresses 4320 (10E0h) through 8191 (1FFFh) are invalid, out of bounds, do not exist in the device, and cannot be addressed.

Notes: 4. BA[8] is the plane-select bit:

Plane 0: BA[8] = 0 Plane 1: BA[8] = 1

**Notes: 5.** LA0 is the LUN-select bit. It is present only when two LUNs are shared on the target; otherwise, it should be held LOW.

LUN 0: LA0 = 0 LUN 1: LA0 = 1

| Mode          | CE# | CLE | ALE | WE# | RE# | DQS | DQx    | WP#                              | Notes |

|---------------|-----|-----|-----|-----|-----|-----|--------|----------------------------------|-------|

| Standby       | н   | X   | Х   | X   | Х   | Х   | Х      | 0V/V <sub>CCQ</sub> <sup>2</sup> | 2     |

| Bus idle      | L   | X   | X   | Н   | Н   | X   | Х      | X                                |       |

| Command input | L   | Н   | L   | l   | Н   | X   | input  | н                                |       |

| Address input | L   | L   | Н   | ٦F  | Н   | X   | input  | н                                |       |

| Data input    | L   | L   | L   | ٦F  | н   | X   | input  | Н                                |       |

| Data output   | L   | L   | L   | н   | ₹   | X   | output | X                                |       |

| Write protect | X   | X   | X   | X   | X   | X   | X      | L                                |       |

### Mode Selection Table

*Notes: 1.* DQS is tri-stated when the asynchronous interface is active.

*Notes: 2.* WP# should be biased to CMOS LOW or HIGH for standby.

**Notes: 3.** Mode selection settings for this table: H = Logic level HIGH; L = Logic level LOW; X = VIH or VIL.

*Notes: 2.* When using the synchronous interface, CA0 is forced to 0 internally; one data cycle always returns one even byte and one odd byte.

| Command                            | 1 <sup>st</sup><br>Cycle | Number of<br>Valid<br>Address<br>Cycles | Data<br>Input<br>Cycles | 2 <sup>nd</sup> Cycle | Valid While<br>Selected<br>LUN<br>is Busy1 | Valid While<br>Other<br>LUNs<br>are Busy2 |

|------------------------------------|--------------------------|-----------------------------------------|-------------------------|-----------------------|--------------------------------------------|-------------------------------------------|

| PAGE READ                          | 00h                      | 5                                       | -                       | 30h                   |                                            | Yes                                       |

| READ for COPY BACK                 | 00h                      | 5                                       |                         | 35h                   |                                            | Yes                                       |

| SEQUENTIAL CACHE READ              | 31h                      | 0                                       | -                       | -                     |                                            | Yes                                       |

| RANDOM CACHE READ                  | 00h                      | 5                                       | -                       | 31h                   |                                            | Yes                                       |

| LAST ADDRESS CACHE READ            | 3Fh                      | 0                                       | -                       | -                     |                                            | Yes                                       |

| READ ID                            | 90h                      | 1                                       | -                       | -                     |                                            |                                           |

| READ STATUS                        | 70h                      | 0                                       | -                       | -                     | Yes                                        |                                           |

| RESET                              | FFh                      | 0                                       | -                       | -                     | Yes                                        | Yes                                       |

| PAGE PROGRAM                       | 80h                      | 5                                       | Yes                     | 10h                   |                                            | Yes                                       |

| PROGRAM for COPY BACK              | 85h                      | 5                                       | Optional                | 10h                   |                                            | Yes                                       |

| CACHE PROGRAM                      | 80h                      | 5                                       | Yes                     | 15h                   |                                            | Yes                                       |

| BLOCK ERASE                        | 60h                      | 3                                       | -                       | D0h                   |                                            | Yes                                       |

| READ PARAMETER PAGE                | ECh                      | 1                                       | -                       | -                     |                                            |                                           |

| READ UNIQUE ID                     | EDh                      | 1                                       | -                       | -                     |                                            |                                           |

| GET FEATURES                       | EEh                      | 1                                       | -                       | -                     |                                            |                                           |

| SET FEATURES                       | EFh                      | 1                                       | 4                       | -                     |                                            |                                           |

| READ STATUS ENHANCED               | 78h                      | 3                                       | -                       | -                     | Yes                                        | Yes                                       |

| READ PAGE MULTIPLANE               | 00h                      | 5                                       | -                       | 32h                   |                                            | Yes                                       |

| TWO PLANE READ FOR COPY<br>BACK    | 00h                      | 5                                       | -                       | 32h                   |                                            | Yes                                       |

| TWO PLANE RANDOM DATA<br>READ      | 00H                      | 5                                       | -                       | 31h                   |                                            | Yes                                       |

| TWO PLANE PROGRAM                  | 80h                      | 5                                       | Yes                     | 11h                   |                                            | Yes                                       |

| CACHE PROGRAM                      | 80h                      | 5                                       | Yes                     | 15h                   |                                            | Yes                                       |

| TWO PLANE PROGRAM FOR<br>COPY BACK | 85h                      | 5                                       | Optional                | 11h                   |                                            | Yes                                       |

| ERASE BLOCK MULTI-PLANE            | 60h                      | 3                                       | -                       | D1h                   |                                            | Yes                                       |

*Note 1:* RANDOM DATA INPUT and RANDOM DATA OUTPUT command is only to be used within a page. *Note 2:* Any commands that are not in the above table are considered as undefined and are prohibited as inputs. *Note 3:* Do not cross plane address boundaries when using Copy Back Read and Program for copy back.

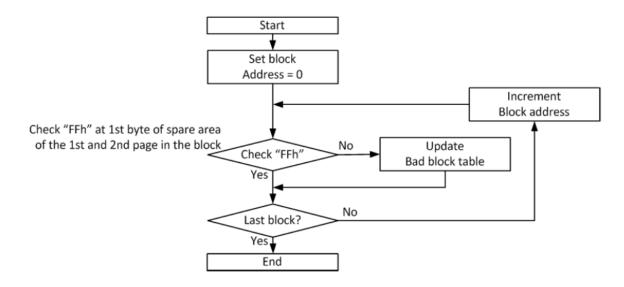

### Invalid Block Management

The H7A2AG21C1CX may have initial invalid blocks when it ships from factory. Also, additional invalid blocks may develop during the use of the device. Nvb represents the minimum number of valid blocks in the total number of available blocks(see below table). An invalid block is defined as blocks that contain one or more bad bits. Block 0, block address 00h is guaranteed to be a valid block at the time of shipment.

| Parameter          | Symbol | Min  | Max  | Unit   |

|--------------------|--------|------|------|--------|

| Valid block number | Nvb    | 1998 | 2048 | blocks |

### Initial Invalid Blocks

Initial invalid blocks are defined as blocks that contain one or more invalid bits when shipped from factory.

Although the device contains initial invalid blocks, a valid block of the device is of the same quality and reliability as all valid blocks in the device with reference to AC and DC specifications. The H7A2AG21C1CX has internal circuits to isolate each block from other blocks and therefore, the invalid blocks will not affect the performance of the entire device.

Before the device is shipped from the factory, it will be erased and invalid blocks are marked. All initial invalid blocks are marked with non-FFh at the first byte of spare area on the 1st or 2nd page. The initial invalid block information cannot be recovered if inadvertently erased. Therefore, software should be created to initially check for invalid blocks by reading the marked locations before performing any program or erase operation, and create a table of initial invalid blocks as following flow chart.

#### flow chart of create initial invalid block table

Additional invalid blocks may develop in the device during its life cycle. Following the procedures herein is required to guarantee reliable data in the device.

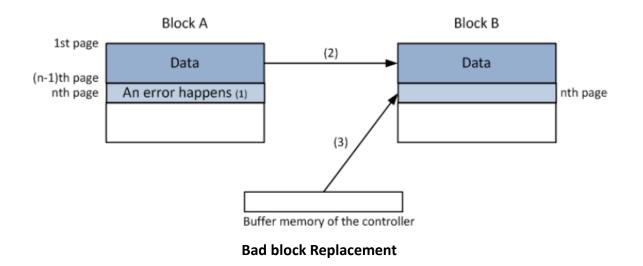

After each program and erase operation, check the status read to determine if the operation failed. In case of failure, a block replacement should be done with a bad-block management algorithm. The system has to use a minimum 1-bit ECC per 528 bytes of data to ensure data recovery.

| Operation | Detection and recommended procedure                       |  |  |

|-----------|-----------------------------------------------------------|--|--|

| Erase     | Status read after erase $\rightarrow$ Block Replacement   |  |  |

| Program   | Status read after program $\rightarrow$ Block Replacement |  |  |

| Read      | Verify ECC $\rightarrow$ ECC correction                   |  |  |

*Note 1:* An error happens in the nth page of block A during program or erase operation.

- *Note 2:* Copy the data in block A to the same location of block B which is valid block.

- *Note 3:* Copy the nth page data of block A in the buffer memory to the nth page of block B

- Note 4: Creating or updating bad block table for preventing further program or erase to block A

### Addressing in program operation

The pages within the block have to be programmed sequentially from LSB (least significant bit) page to the MSB (most significant bit) within the block. The LSB is defined as the start page to program, does not need to be page 0 in the block. Random page programming is prohibited.

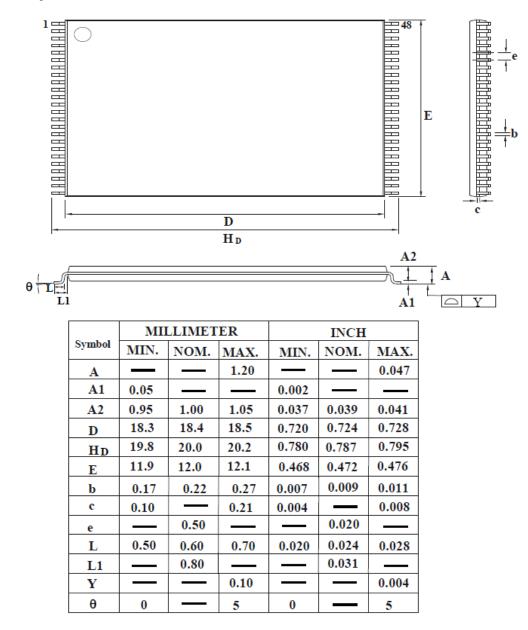

**TSOP 48-pin 12x20**

### **Revision History**

| Revision No. | History              | Draft Date | Editor        | Remark |

|--------------|----------------------|------------|---------------|--------|

| 0.1          | Initial Release.     | Nov. 2018  | Ternence Chen | N/A    |

| 1.0          | First SPEC. Release. | Nov. 2018  | Ternence Chen | N/A    |