## 128Mb (2M×4Bank×16) Synchronous DRAM

#### **Descriptions**

H2A11281636B is a high-speed synchronous dynamic random access memory (SDRAM), organized as 2M words x 4 banks x 16 bits. H2A11281636B delivers a data bandwidth of up to 166M words per second

Accesses to the SDRAM are burst oriented. Consecutive memory location in one page can be accessed at a burst length of 1, 2, 4, 8 or full page when a bank and row is selected by an ACTIVE command..

By having a programmable Mode Register, the system can change burst length, latency cycle, interleave or sequential burst to maximize its performance. H2A11281636B is ideal for main memory in high performance applications.

#### **Features**

- 3.3V +/- 0.3V Power Supply

- Up to 166 MHz Clock Frequency

- 2,097,152 Words x 4 banks x 16 bits organization

- Self Refresh Mode

- CAS Latency: 2 and 3

- Burst Length: 1,2,4,8 and full page

- Burst Read, Single Writes Mode

- Byte Data Controlled by LDQM, UDQM

- Auto-precharge and Controlled Precharge

- 4K Refresh cycles / 64 mS

- Interface: LVTTL

- Packaged in TFBGA 54 Ball (8x8 mm<sup>2</sup>)

### **Ordering Information**

| Part No         | Organization | Max. Frequency | Max. Frequency Package |            |

|-----------------|--------------|----------------|------------------------|------------|

| H2A11281636B8VC | 8M X 16      | 133MHz @ CL3   | 54Ball BGA, 8x8mm      | Commercial |

| H2A11281633BMVC | 8M X 16      | 166MHz @ CL3   | 54Ball BGA, 8x8mm      | Commercial |

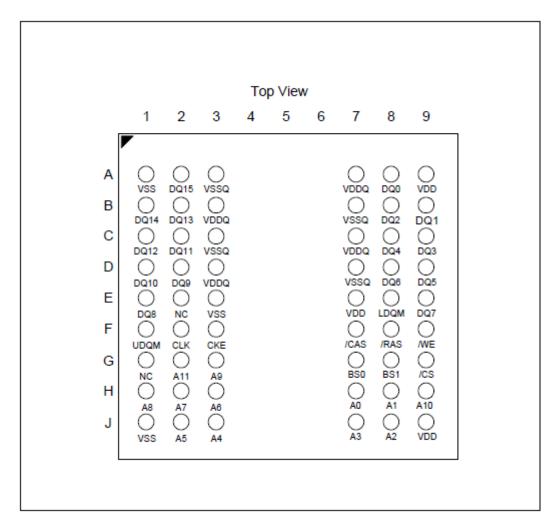

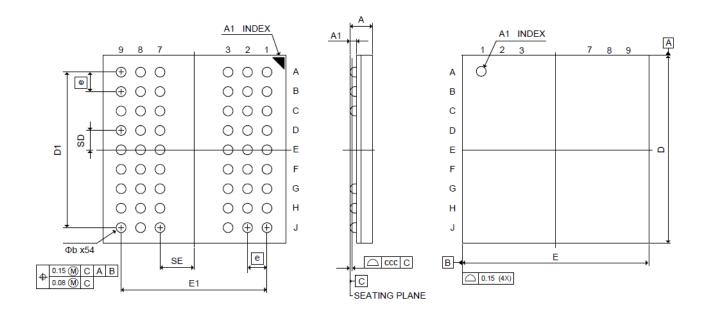

## **Ball Configuration**

TFBGA 54 Ball (8x8 mm<sup>2</sup>)

# Ball Description (Simplified)

| Ball Location   | Name     | Function Description                                                                                         |

|-----------------|----------|--------------------------------------------------------------------------------------------------------------|

|                 |          | (Address)                                                                                                    |

| H7, H8, J8, J7, |          | Multiplexed pins for row and column address. Row address:                                                    |

| J3,J2, H3, H2,  | A0~A11   | A0-A11. Column address: A0-A8. A10 is sampled during a                                                       |

| H1,G3, H9, G2   |          | precharge command to determine if all banks are to be                                                        |

|                 |          | precharged or bank selected by BS0, BS1.                                                                     |

| 07.00           | 500 504  | (Bank Selet)                                                                                                 |

| G7, G8          | BS0, BS1 | Select bank to activate during row address latch time, or bank                                               |

| A8, B9, B8, C9, |          | to read/write during address latch time.  (Data Input/Output)                                                |

|                 | DQ0~DQ   | Multiplexed pins for data output and input.                                                                  |

| C8, D9, D8, E9, |          | ividitiplexed pills for data output and input.                                                               |

| E1, D2, D1, C2, | 15       |                                                                                                              |

| C1, B2, B1, A2  |          |                                                                                                              |

|                 |          | (Chip Select)                                                                                                |

| G9              | CS       | Disable or enable the command decoder. When command decoder is disabled, new command is ignored and previous |

|                 |          | operation continues.                                                                                         |

|                 |          | (Row Address Strobe)                                                                                         |

| F8              | RAS      | Command input. When sampled at the rising edge of                                                            |

| ГО              | KAS      | the clock RAS, CAS and WE define the operation to be                                                         |

|                 |          | executed.                                                                                                    |

| F7              | CAS      | (Column Address Strobe)                                                                                      |

|                 |          | Referred to RAS                                                                                              |

| F9              | WE       | (Write Enable)                                                                                               |

|                 |          | Referred to RAS                                                                                              |

|                 | UDQM,    | (Input/Output Mask) The output buffer is placed at Hi-Z (with latency of 2) when                             |

| F1, E8          | LDQM     | DQM is sampled high in read cycle. In write cycle, sampling                                                  |

|                 |          | DQM high will block the write operation with zero latency.                                                   |

|                 |          | (Clock Inputs)                                                                                               |

| F2              | CLK      | System clock used to sample inputs on the rising edge of                                                     |

|                 |          | clock.                                                                                                       |

|                 |          | (Clock Enable)                                                                                               |

| F3              | CKE      | CKE controls the clock activation and deactivation. When                                                     |

|                 |          | CKE is low, Power Down mode, Suspend mode, or Self                                                           |

|                 |          | Refresh mode is entered.                                                                                     |

| A9, E7, J9      | VDD      | (Power)                                                                                                      |

|                 |          | Power for input buffers and logic circuit inside DRAM.                                                       |

| A1, E3, J1      | VSS      | (Ground) Ground for input buffers and logic circuit inside DRAM.                                             |

|                 |          | (Power for I/O buffer)                                                                                       |

| A7, B3, C7, D3  | VDDQ     | Separated power from VDD, to improve DQ noise immunity.                                                      |

|                 |          | (Ground for I/O)                                                                                             |

| A3, B7, C3, D7  | VSSQ     | Separated ground from VSS, to improve DQ noise immunity.                                                     |

|                 |          | (No Connection)                                                                                              |

| E2, G1          | NC       | No connection                                                                                                |

#### Absolute Maximum Rating

| Symbol            | Item                        | Rati                                             | Units |    |  |

|-------------------|-----------------------------|--------------------------------------------------|-------|----|--|

| $V_{IN}, V_{OUT}$ | Input, Output Voltage       | $-0.5 \sim V_{DD} + 0.5 (\le 4.6 \text{V max.})$ |       | V  |  |

| $V_{DD}, V_{DDQ}$ | Power Supply Voltage        | -0.5 ~                                           | +4.6  | V  |  |

| T <sub>OP</sub>   | Operating Temperature Range | Operating Temperature Range Commercial 0 ~ +70   |       |    |  |

| T <sub>STG</sub>  | Storage Temperature Range   | -55 ~ +                                          | -150  | °C |  |

| TSOLDER           | Soldering Temperature (10s) | 260                                              | )     | °C |  |

| $P_{D}$           | Power Dissipation           | 1                                                |       | W  |  |

| I <sub>os</sub>   | Short Circuit Current       | 50                                               | mA    |    |  |

**Note:** Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and reliability of the device.

## Capacitance ( $V_{CC}$ =3.3V, f=1MHz, $T_A$ =25 $^{\circ}C$ )

| Symbol    | Parameter                                                                 | Min. | Тур. | Max. | Units |

|-----------|---------------------------------------------------------------------------|------|------|------|-------|

| $C_{CLK}$ | Clock Capacitance                                                         | -    | -    | 3.5  | pF    |

| Cı        | Input Capacitance for CLK, CKE, Address, /CS, /RAS, /CAS, /WE, DQML, DQMU | -    | -    | 3.8  | pF    |

| Co        | Input / Output Capacitance                                                | -    | -    | 6.5  | pF    |

# Recommended DC Operating Conditions ( $T_A$ =-0°C ~+70°C)

| Symbol          | Parameter                             | Min. | Тур. | Max.                 | Units |

|-----------------|---------------------------------------|------|------|----------------------|-------|

| $V_{DD}$        | Power Supply Voltage                  | 3.0  | 3.3  | 3.6                  | V     |

| $V_{DDQ}$       | Power Supply Voltage (for I/O Buffer) | 3.0  | 3.3  | 3.6                  | V     |

| V <sub>IH</sub> | Input Logic High Voltage              | 2.0  | -    | V <sub>DD</sub> +0.3 | V     |

| $V_{IL}$        | Input Logic Low Voltage               | -0.3 | -    | 0.8                  | V     |

Note: \* All voltages referred to VSS.

<sup>\*</sup> VIH (max.) = VDD / VDDQ +1.5V for pulse width  $\leq$  5ns

<sup>\*</sup> VIL (min.) = VDD / VSSQ -1.5V for pulse width  $\leq$  5ns

# Recommended DC Operating Conditions

$(V_{DD}=3.3V\pm0.3V, T_{A}=0^{\circ}C \sim 70^{\circ}C)$

| Bananata                                                                                          | _                                           | 0      | Ма     | IX.    | 11    |

|---------------------------------------------------------------------------------------------------|---------------------------------------------|--------|--------|--------|-------|

| Paramete                                                                                          | ſ                                           | Symbol | 166MHz | 133MHz | Units |

| Operating Current tck = min., trc = min. Active precharge command cycling without burst operation | 1 Bank operation                            | IDD1   | 50     | 45     | mA    |

| Standby Current                                                                                   | CKE = VIH                                   | IDD2   | 20     | 0      | mA    |

| tck = min., CS = VIH VIH /L = VIH (min.) /VIL (max.) Bank: inactive state                         | CKE = V <sub>IL</sub><br>(Power Down mode)  | IDD2P  | 2      | !      | mA    |

| Standby Current                                                                                   | CKE = VIH                                   | IDD2S  | 1:     | mA     |       |

| CLK = VIL, CS = VIH  VIH/L = VIH (min.) /VIL (max.)  Bank: inactive state                         | CKE = V <sub>IL</sub><br>(Power Down mode)  | IDD2PS | 2      |        | mA    |

| No Operating Current                                                                              | CKE = VIH                                   | IDD3   | 35     | 30     | mA    |

| tck = min., CS = VIH (min.) Bank: active state (4 Banks)                                          | CKE = V <sub>I</sub> L<br>(Power Down mode) | IDD3P  | 1:     | 2      | mA    |

| Burst Operating Current (tck = min.) Read/ Write command cycling                                  |                                             | IDD4   | 75     | 70     | mA    |

| Auto Refresh Current (tck = min.) Auto refresh command cycling                                    |                                             | IDD5   | 65     | 60     | mA    |

| Self Refresh Current Self refresh mode (CKE = 0.2V)                                               |                                             | IDD6   | 2      | 2      | mA    |

# Recommended DC Operating Conditions (Continued)

| Symbol          | Parameter                 | Test Conditions                                                                  | Min. | Max. | Units |

|-----------------|---------------------------|----------------------------------------------------------------------------------|------|------|-------|

| I <sub>IL</sub> | Input Leakage Current     | $0 \le V_I \le V_{DDQ}$ , $V_{DDQ} = V_{DD}$<br>All other pins not under test=0V | -5   | 5    | uA    |

| I <sub>OL</sub> | Output Leakage Current    | 0≤V <sub>O</sub> ≤V <sub>DDQ</sub> , D <sub>OUT</sub> is disabled                | -5   | 5    | uA    |

| V <sub>OH</sub> | High Level Output Voltage | I <sub>O</sub> =-4mA                                                             | 2.4  | -    | V     |

| V <sub>OL</sub> | Low Level Output Voltage  | I <sub>O</sub> =+4mA                                                             | 1    | 0.4  | V     |

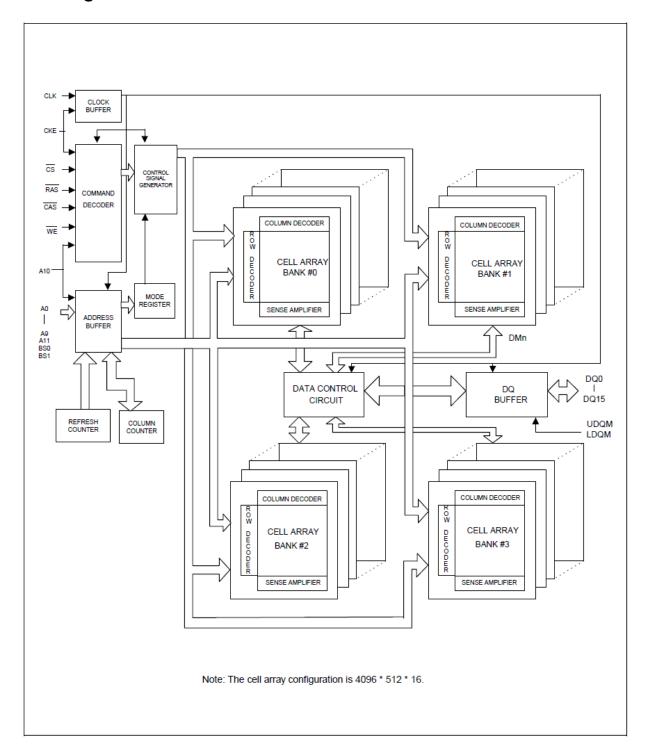

### **Block Diagram**

# AC Test Characteristics and Operating Conditions

$(V_{DD}=3.3V\pm0.3V, T_{A}=0^{\circ}C \sim 70^{\circ}C)$

|                                         | DADAMETED  |       | 166  | 6MHz   | 13   | 3MHz   |      |       |

|-----------------------------------------|------------|-------|------|--------|------|--------|------|-------|

| PARAMETER                               |            | SYM.  | Min. | Max.   | Min. | Max.   | Unit | Notes |

| Ref/Active to Ref/Active Command Per    | riod       | tRC   | 60   |        | 65   |        |      |       |

| Active to Precharge Command Period      |            | tRAS  | 42   | 100000 | 45   | 100000 | nS   |       |

| Active to Read/Write Command Delay Time | е          | tRCD  | 15   |        | 20   |        |      |       |

| Read/Write(a) to Read/Write(b)Comma     | and Period | tCCD  | 1    |        | 1    |        | tCK  |       |

| Precharge to Active(b) Command Period   | od         | tRP   | 15   |        | 20   |        | ~ C  |       |

| Active(a) to Active(b) Command Period   | d          | tRRD  | 12   |        | 15   |        | nS   |       |

| Write Recovery Time                     | CL* = 2    | tWR   | 2    |        | 2    |        | tCK  |       |

| Write Recovery Time                     | CL* = 3    | LVVIX | 2    |        | 2    |        | ick  |       |

| CLK Cycle Time                          | CL* = 2    | tCK   | 7.5  | 1000   | 10   | 1000   |      |       |

| CER Cycle Time                          | CL* = 3    | ion   | 6    | 1000   | 7.5  | 1000   |      |       |

| CLK High Level Width                    |            | tCH   | 2    |        | 2.5  |        |      | 8     |

| CLK Low Level Width                     |            | tCL   | 2    |        | 2.5  |        |      | 8     |

| Access Time from CLK                    | CL* = 2    | tAC   |      | 6      |      | 6      |      | 9     |

|                                         | CL* = 3    | IAC   |      | 5      |      | 5.4    |      | 9     |

| Output Data Hold Time                   |            | tOH   | 3    |        | 3    |        |      | 9     |

| Output Data High Impedance Time         | CL* = 2    | tHZ   |      | 6      |      | 6      |      | 7     |

| Output Data Flight Impedance Time       | CL* = 3    | li iZ |      | 5      |      | 5.4    |      |       |

| Output Data Low Impedance Time          |            | tLZ   | 0    |        | 0    |        | nS   | 9     |

| Power Down Mode Entry Time              |            | tSB   | 0    | 6      | 0    | 7.5    | 110  |       |

| Transition Time of CLK (Rise and Fall)  |            | tΤ    |      | 1      |      | 1      |      |       |

| Data-in-Set-up Time                     |            | tDS   | 1.5  |        | 1.5  |        |      | 8     |

| Data-in Hold Time                       |            | tDH   | 0.8  |        | 0.8  |        |      | 8     |

| Address Set-up Time                     |            | tAS   | 1.5  |        | 1.5  |        |      | 8     |

| Address Hold Time                       |            | tAH   | 0.8  |        | 0.8  |        |      | 8     |

| CKE Set-up Time                         |            | tCKS  | 1.5  |        | 1.5  |        |      | 8     |

| CKE Hold Time                           |            | tCKH  | 0.8  |        | 0.8  |        |      | 8     |

| Command Set-up Time                     |            | tCMS  | 1.5  |        | 1.5  |        |      | 8     |

| Command Hold Time                       |            | tCMH  | 0.8  |        | 0.8  |        |      | 8     |

| Refresh Time                            |            | tREF  |      | 64     |      | 64     | mS   |       |

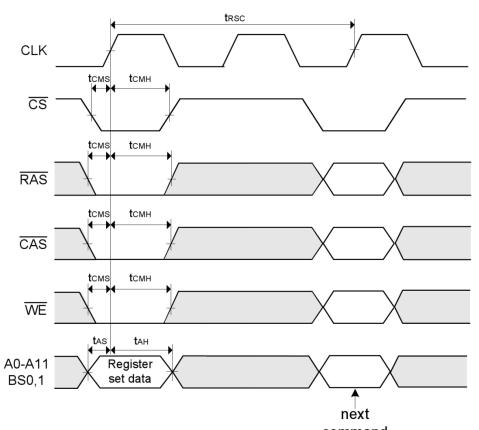

| Mode Register Set Cycle Time            |            | tRSC  | 2    |        | 2    |        | tCK  |       |

| Exit self refresh to ACTIVE command     |            | tXSR  | 72   |        | 75   |        | nS   |       |

#### Notes:

- 1. Operation exceeds "Absolute Maximum Ratings" may cause permanent damage to the devices.

- 2. All voltages are referenced to VSS.

- 3. These parameters depend on the cycle rate and listed values are measured at a cycle rate with the minimum values of tCK and tRC.

- 4. These parameters depend on the output loading conditions. Specified values are obtained with output open.

- 5. Power up sequence is further described in the "Functional Description" section.

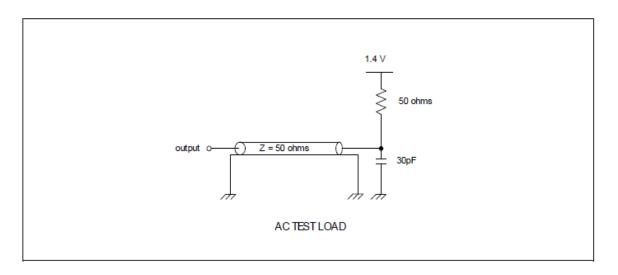

- 6. AC test load diagram.

- 7. tHZ defines the time at which the outputs achieve the open circuit condition and is not referenced to output level.

- 8. Assumed input rise and fall time (tT) = 1nS.If tr & tf is longer than 1nS, transient time compensation should be considered, i.e., [(tr + tf)/2-1]nS should be added to the parameter.

- 9. If clock rising time (tT) is longer than 1nS, (tT/2-0.5)nS should be added to the parameter.

## Address Input for Mode Register Set

|     |     |                |          | command    |               |                |

|-----|-----|----------------|----------|------------|---------------|----------------|

| A0  |     |                |          |            |               | _ength         |

|     |     | D              | ◀        | – A2 A1 A0 | Sequential    | Interleave     |

| A1  |     | Burst Length   |          | 0 0 0      | 1             | 1              |

| A2  |     |                |          | 0 0 1      | 2             | 2              |

|     |     |                | -        | 0 1 0      | 4             | 4              |

| A3  | Ad  | ldressing Mode | ◀        | 0 1 1      | 8             | 8              |

|     |     |                | 1        | 1 0 0      | D             |                |

| A4  |     |                |          | 1 0 1      | Reserved      | Reserved       |

| A5  |     | CAS Latency    | ←──      | 1 1 0      | Full Page     |                |

|     |     | •              |          | 1 1 1      |               |                |

| A6  |     |                |          | - A3       | Addressi      |                |

| A7  | "0" | (Test Mode)    | 1        | 0          |               | ential         |

|     |     | (Test Wisde)   |          | 1          | Inter         | eave           |

| A8  | "0" | Reserved       |          | - A6 A5 A4 | CAS L         | atency         |

| A9  |     | Write Mode     | <b> </b> | 0 0 0      | Rese          | erved          |

|     |     | I              |          | 0 0 1      | Rese          | erved          |

| A10 | "0" |                |          | 0 1 0      | 2             | 2              |

| A11 | "0" |                |          | 0 1 1      | _ 3           |                |

| Α11 | U   | Reserved       |          | 1 0 0      | Rese          | erved          |

| BS0 | "0" |                | l L      | – A9       | Single Wi     | rite Mode      |

| BS1 | "0" |                |          | 0          | Burst read an |                |

|     |     |                | J        | 1          | Burst read an | d single write |

<sup>\* &</sup>quot;Reserved" should stay "0" during MRS cycle.

## Burst Type (A3)

| Burst Length | A2 | <b>A1</b> | A0 | Sequential Addressing | Interleave Addressing |

|--------------|----|-----------|----|-----------------------|-----------------------|

| 2            | Х  | Χ         | 0  | 0 1                   | 0 1                   |

| 2            | Х  | Χ         | 0  | 1 0                   | 1 0                   |

|              | Х  | 0         | 0  | 0123                  | 0123                  |

| 4            | Х  | 0         | 1  | 1230                  | 1032                  |

| 4            | Х  | 1         | 0  | 2301                  | 2301                  |

|              | Х  | 1         | 1  | 3012                  | 3210                  |

|              | 0  | 0         | 0  | 01234567              | 01234567              |

|              | 0  | 0         | 1  | 12345670              | 10325476              |

|              | 0  | 1         | 0  | 23456701              | 23016745              |

| 8            | 0  | 1         | 1  | 34567012              | 32107654              |

| 0            | 1  | 0         | 0  | 45670123              | 45670123              |

|              | 1  | 0         | 1  | 56701234              | 54761032              |

|              | 1  | 1         | 0  | 67012345              | 67452301              |

|              | 1  | 1         | 1  | 70123456              | 76543210              |

| Full Page*   | n  | n         | n  | Cn Cn+1 Cn+2          | -                     |

<sup>\*</sup> Page length is a function of I/O organization and column addressing ×16 (CA0 ~ CA7):Full page = 256bits

#### 1. Command Truth Table

| Command                    | Cymbol | CK  | Е | /CS | /RAS | /CAS | /WE  | BA0, | A10 | A11,   |

|----------------------------|--------|-----|---|-----|------|------|------|------|-----|--------|

| Command                    | Symbol | n-1 | n | 2   | /KAS | /CAS | /VVE | BA1  | AIU | A9~A10 |

| Ignore Command             | DESL   | Н   | Х | Н   | Χ    | Х    | Х    | Χ    | Χ   | X      |

| No Operation               | NOP    | Н   | Х | L   | Н    | Н    | Н    | Χ    | Х   | Х      |

| Burst Stop                 | BSTH   | Н   | Χ | L   | Н    | Н    | L    | Χ    | Х   | Х      |

| Read                       | READ   | Н   | Х | L   | Н    | L    | Н    | V    | L   | V      |

| Read with Auto Pre-charge  | READA  | Н   | Χ | L   | Н    | L    | Н    | V    | Н   | V      |

| Write                      | WRIT   | Н   | Х | L   | Н    | L    | L    | V    | L   | V      |

| Write with Auto Pre-charge | WRITA  | Н   | Х | L   | L    | Н    | Н    | V    | Н   | V      |

| Bank Activate              | ACT    | Н   | Χ | L   | L    | Н    | Н    | V    | V   | V      |

| Pre-charge Select Bank     | PRE    | Н   | Χ | L   | L    | Н    | L    | V    | L   | Х      |

| Pre-charge All Banks       | PALL   | Н   | Х | L   | L    | Н    | L    | Х    | Н   | Х      |

| Mode Register Set          | MRS    | Н   | Х | L   | L    | L    | L    | L    | L   | V      |

H = High level, L = Low level, X = High or Low level (Don't care), V = Valid data input

#### 2. DQM Truth Table

| Command                               | Cymhol | CI  | KE | /CS      |

|---------------------------------------|--------|-----|----|----------|

| Command                               | Symbol | n-1 | n  | /03      |

|                                       |        |     |    |          |

| Data Write/Output Enable              | ENB    | Н   | Х  | Н        |

| Data Mask/Output Disable              | MASK   | Н   | Х  | L        |

|                                       |        |     |    | <u> </u> |

| Upper Byte Write Enable/Output Enable | BSTH   | Н   | Х  | L        |

| Read                                  | READ   | Н   | Х  | L        |

| Read with Auto Pre-charge             | READA  | Н   | Х  | L        |

| Write                                 | WRIT   | Н   | Х  | L        |

| Write with Auto Pre-charge            | WRITA  | Н   | Х  | L        |

| Bank Activate                         | ACT    | Н   | Х  | L        |

| Pre-charge Select Bank                | PRE    | Н   | Х  | L        |

| Pre-charge All Banks                  | PALL   | Н   | Х  | L        |

| Mode Register Set                     | MRS    | Н   | Х  | L        |

H = High level, L = Low level, X = High or Low level (Don't care), V = Valid data input

### 3. CKE Truth Table

| ltem             | Command                  | Symbo | CK | Ε | /CS | /RA | /CA | /WE | Addr. |

|------------------|--------------------------|-------|----|---|-----|-----|-----|-----|-------|

| iteiii           | Command                  | I     | n- | n | /63 | S   | S   | /VV | Addi. |

| Activating       | Clock Suspend Mode Entry |       | Н  | L | Χ   | Χ   | Χ   | Х   | Χ     |

| Any              | Clock Suspend Mode       |       | L  | L | Х   | X   | X   | Χ   | Χ     |

| Clock<br>Suspend | Clock Suspend Mode Exit  |       | L  | Н | Х   | Х   | Х   | Х   | Х     |

| Idle             | CBR Refresh Command      | REF   | Н  | Н | L   | L   | L   | Н   | Χ     |

| Idle             | Self Refresh Entry       | SELF  | Н  | L | L   | L   | L   | Η   | X     |

| Self Refresh     | Self Refresh Exit        |       | L  | Н | L   | Η   | Η   | Н   | Х     |

| Sell Reflesh     | Sell Reliesh Exit        |       | L  | Η | Н   | Χ   | Χ   | Χ   | X     |

| Idle             | Power Down Entry         |       | Н  | L | Х   | Χ   | Χ   | Χ   | Х     |

| Power Down       | Power Down Exit          |       | L  | Н | Х   | Χ   | Χ   | Χ   | Χ     |

**Remark** H = High level, L = Low level, X = High or Low level (Don't care)

| Current<br>State | /CS | /R | /C | /W | Addr.     | Command                            | Action                                                       |

|------------------|-----|----|----|----|-----------|------------------------------------|--------------------------------------------------------------|

|                  | Н   | Х  | Х  | Х  | Х         | DESL                               | Nop or power down (Note 8)                                   |

|                  | L   | Н  | Н  | Х  | Х         | NOP or BST                         | Nop or power down (Note 8)                                   |

|                  | L   | Н  | L  | Н  | BA/CA/A10 | READ/READA                         | ILLEGAL (Note 9)                                             |

|                  | L   | Н  | L  | L  | BA/CA/A10 | WRIT/WRITA                         | ILLEGAL (Note 9)                                             |

| Idle             | L   | L  | Н  | Н  | BA/RA     | ACT                                | Row activating                                               |

|                  | L   | L  | Н  | L  | BA, A10   | PRE/PALL                           | Nop                                                          |

|                  | L   | L  | L  | Н  | Х         | REF/SELF                           | Refresh or self refresh (Note 10)                            |

|                  | L   | L  | L  | L  | Op-Code   | MRS                                | Mode register accessing                                      |

|                  | Н   | Χ  | Χ  | Χ  | X         | DESL                               | Nop                                                          |

|                  | L   | Н  | Н  | Х  | Х         | NOP or BST                         | Nop (Note 11)                                                |

|                  | L   | Н  | L  | Н  | BA/CA/A10 | READ/READA                         | Begin read: Determine AP (Note 11)                           |

| Row              | L   | Н  | L  | L  | BA/CA/A10 | WRIT/WRITA                         | Begin write: Determine AP (Note 11)                          |

| Active           | L   | L  | Н  | Н  | BA/RA     | ACT                                | ILLEGAL <sup>(Note 9)</sup>                                  |

|                  | L   | L  | Н  | L  | BA, A10   | PRE/PALL                           | Pre-charge (Note 12)                                         |

|                  | L   | L  | L  | Н  | Х         | REF/SELF                           | ILLEGAL (Note 10)                                            |

|                  | L   | L  | L  | L  | Op-Code   | MRS                                | ILLEGAL                                                      |

|                  | Н   | Χ  | Χ  | Χ  | X         | DESL                               | Continue burst to end → Row active                           |

|                  | L   | Н  | Н  | Н  | X         | NOP                                | Continue burst to end $\rightarrow$ Row active               |

|                  | L   | Н  | Н  | L  | X         | X BST Burst stop $\rightarrow$ Row |                                                              |

|                  | L   | Н  | L  | Н  | BA/CA/A10 | READ/READA                         | Terminate burst, new read: Determine AP (Note 13)            |

| Read             | L   | L  | L  | L  | BA/CA/A10 | WRIT/WRITA                         | Terminate burst, start write: Determine AP (Note 13, 14)     |

|                  | L   | L  | Н  | Н  | BA/RA     | ACT                                | ILLEGAL (Note 9)                                             |

|                  | L   | L  | Н  | L  | BA, A10   | PRE/PALL                           | Terminate burst, pre-charging (Note 10)                      |

|                  | L   | L  | L  | Н  | X         | REF/SELF                           | ILLEGAL                                                      |

|                  | L   | L  | L  | L  | Op-Code   | MRS                                | ILLEGAL                                                      |

|                  | Н   | Х  | Х  | Χ  | Х         | DESL                               | Continue burst to end → Write recovering                     |

|                  | L   | Н  | Н  | Н  | Х         | NOP                                | Continue burst to end → Write recovering                     |

|                  | L   | Н  | Н  | L  | X         | BST                                | Burst stop → Row active                                      |

|                  | L   | Н  | L  | Н  | BA/CA/A10 | READ/READA                         | Terminate burst, start read: Determine AP 7, 8 (Note 13, 14) |

| Write            | L   | L  | L  | L  | BA/CA/A10 | WRIT/WRITA                         | Terminate burst, new write:  Determine AP 7 (Note 13)        |

|                  | L   | L  | Н  | Н  | BA/RA     | ACT                                | ILLEGAL (Note 9)                                             |

|                  | L   | L  | Н  | L  | BA, A10   | PRE/PALL                           | Terminate burst, pre-charging (Note 15)                      |

|                  | L   | L  | L  | Н  | Х         | REF/SELF                           | ILLEGAL                                                      |

|                  | L   | L  | L  | L  | Op-Code   | MRS                                | ILLEGAL                                                      |

Remark H = High level, L = Low level, X = High or Low level (Don't care)

# 4. Operative Command Table (Continued) (Note 7)

| Current<br>State  | /CS | /R | /C | /W | Addr.     | Command    | Action                                                        |

|-------------------|-----|----|----|----|-----------|------------|---------------------------------------------------------------|

|                   | Н   | Х  | Х  | Х  | Х         | DESL       | Continue burst to end → Pre-charging                          |

|                   | L   | Н  | Н  | Н  | Х         | NOP        | Continue burst to end → Pre-charging                          |

|                   | L   | Н  | Н  | L  | X         | BST        | ILLEGAL                                                       |

| Read with         | L   | Н  | L  | Η  | BA/CA/A10 | READ/READA | ILLEGAL (Note 9)                                              |

| AP                | L   | Н  | L  | L  | BA/CA/A10 | WRIT/WRITA | ILLEGAL (Note 9)                                              |

|                   | L   | L  | Н  | Н  | BA/RA     | ACT        | ILLEGAL (Note 9)                                              |

|                   | L   | L  | Н  | L  | BA, A10   | PRE/PALL   | ILLEGAL (Note 9)                                              |

|                   | L   | L  | L  | Н  | Х         | REF/SELF   | ILLEGAL                                                       |

|                   | L   | L  | L  | L  | Op-Code   | MRS        | ILLEGAL                                                       |

|                   | Н   | Х  | Х  | Х  | X         | DESL       | Burst to end → Write recovering with auto pre-charge          |

|                   | L   | Н  | Η  | Η  | X         | NOP        | Continue burst to end → Write recovering with auto pre-charge |

|                   | L   | Η  | Η  | L  | Χ         | BST        | ILLEGAL                                                       |

| Write with        | L   | Τ  | L  | Н  | BA/CA/A10 | READ/READA | ILLEGAL (Note 9)                                              |

| AP                | L   | Н  | L  | L  | BA/CA/A10 | WRIT/WRITA | ILLEGAL (Note 9)                                              |

|                   | L   | L  | Н  | Н  | BA/RA     | ACT        | ILLEGAL (Note 9)                                              |

|                   | L   | L  | Н  | L  | BA, A10   | PRE/PALL   | ILLEGAL (Note 9)                                              |

|                   | L   | L  | L  | Н  | X         | REF/SELF   | ILLEGAL                                                       |

|                   | L   | L  | L  | L  | Op-Code   | MRS        | ILLEGAL                                                       |

|                   | Н   | Χ  | Χ  | Χ  | X         | DESL       | Nop $\rightarrow$ Enter idle after $t_{RP}$                   |

|                   | L   | Η  | Ι  | Ι  | X         | NOP        | Nop $\rightarrow$ Enter idle after $t_{RP}$                   |

|                   | L   | Η  | Н  | L  | X         | BST        | ILLEGAL                                                       |

|                   | L   | Н  | L  | Η  | BA/CA/A10 | READ/READA | ILLEGAL (Note 9)                                              |

| Pre-charging      | L   | Н  | L  | L  | BA/CA/A10 | WRIT/WRITA | ILLEGAL (Note 9)                                              |

|                   | L   | L  | Ι  | Ι  | BA/RA     | ACT        | ILLEGAL (Note 9)                                              |

|                   | L   | L  | Н  | L  | BA, A10   | PRE/PALL   | Nop $\rightarrow$ Enter idle after $t_{RP}$                   |

|                   | L   | L  | L  | Н  | X         | REF/SELF   | ILLEGAL                                                       |

|                   | L   | L  | L  | L  | Op-Code   | MRS        | ILLEGAL                                                       |

|                   | Н   | Х  | Χ  | Χ  | Х         | DESL       | Nop → Enter idle after t <sub>RCD</sub>                       |

|                   | L   | Н  | Н  | Н  | X         | NOP        | Nop → Enter idle after t <sub>RCD</sub>                       |

|                   | L   | Н  | Η  | L  | Х         | BST        | ILLEGAL                                                       |

| Davis             | L   | Н  | L  | Н  | BA/CA/A10 | READ/READA | ILLEGAL (Note 9)                                              |

| Row<br>Activating | L   | Н  | L  | L  | BA/CA/A10 | WRIT/WRITA | ILLEGAL (Note 9)                                              |

|                   | L   | L  | Н  | Н  | BA/RA     | ACT        | ILLEGAL (Note 9, 16)                                          |

|                   | L   | L  | Η  | L  | BA, A10   | PRE/PALL   | ILLEGAL (Note 9)                                              |

|                   | L   | L  | L  | Н  | X         | REF/SELF   | ILLEGAL                                                       |

|                   | L   | L  | L  | L  | Op-Code   | MRS        | ILLEGAL                                                       |

Remark H = High level, L = Low level, X = High or Low level (Don't care), AP = Auto Pre-charge

# 4. Operative Command Table (Continued) (Note 7)

| Current<br>State    | /CS | /R | /C | /W | Addr.                               | Command                       | Action                                        |

|---------------------|-----|----|----|----|-------------------------------------|-------------------------------|-----------------------------------------------|

|                     | Н   | Х  | Х  | Χ  | Х                                   | DESL                          | Nop → Enter row active after t <sub>DPL</sub> |

|                     | L   | Н  | Н  | Н  | X                                   | NOP                           | Nop → Enter row active after t <sub>DPL</sub> |

|                     | L   | Η  | Η  | L  | X                                   | BST                           | Nop → Enter row active after t <sub>DPL</sub> |

|                     | L   | Н  | L  | Н  | BA/CA/A10 READ/READA Start read, De |                               | Start read, Determine AP                      |

| Write<br>Recovering | L   | Н  | L  | L  | BA/CA/A10                           | WRIT/WRITA                    | New write, Determine AP (Note 14)             |

| Recovering          | L   | L  | Η  | Н  | BA/RA                               | ACT                           | ILLEGAL (Note 9)                              |

|                     | L   | L  | Н  | L  | BA, A10                             | PRE/PALL                      | ILLEGAL (Note 9)                              |

|                     | L   | L  | L  | Н  | Х                                   | REF/SELF                      | ILLEGAL                                       |

|                     | L   | L  | L  | L  | Op-Code                             | MRS                           | ILLEGAL                                       |

|                     | Н   | Χ  | Χ  | Χ  | X                                   | DESL                          | Nop → Enter pre-charge after t <sub>DPL</sub> |

|                     | L   | Η  | Η  | Η  | X                                   | NOP                           | Nop → Enter pre-charge after t <sub>DPL</sub> |

|                     | L   | Η  | Η  | L  | X                                   | BST                           | Nop → Enter pre-charge after t <sub>DPL</sub> |

| Write               | L   | Η  | L  | Н  | BA/CA/A10                           | READ/READA                    | ILLEGAL (Note 9, 14)                          |

| Recovering          | L   | Н  | L  | L  | BA/CA/A10                           | WRIT/WRITA                    | ILLEGAL (Note 9)                              |

| with AP             | L   | L  | Н  | Н  | BA/RA                               | ACT                           | ILLEGAL (Note 9)                              |

|                     | L   |    | Η  | L  | BA, A10                             | PRE/PALL                      | ILLEGAL                                       |

|                     | L   | L  | L  | Н  | X                                   | REF/SELF                      | ILLEGAL                                       |

|                     | L   | L  | L  | L  | Op-Code                             | MRS                           | ILLEGAL                                       |

|                     | Н   | Χ  | Χ  | Χ  | X                                   | DESL                          | Nop $\rightarrow$ Enter idle after $t_{RC}$   |

|                     | L   | Н  | Н  | Χ  | X                                   | NOP/BST                       | Nop $\rightarrow$ Enter idle after $t_{RC}$   |

| Refreshing          | L   | Н  | L  | Χ  | X                                   | READ/WRIT                     | ILLEGAL                                       |

|                     | L   | L  | Н  | Χ  | X                                   | ACT/PRE/PALL                  | ILLEGAL                                       |

|                     | L   | L  | L  | Χ  | X                                   | REF/SELF/MRS                  | ILLEGAL                                       |

|                     | Н   | Х  | Х  | Χ  | X                                   | DESL                          | Nop                                           |

| Mode                | L   | Н  | Н  | Н  | X                                   | NOP                           | Nop                                           |

| Register            | L   | Н  | Н  | L  | X                                   | BST                           | ILLEGAL                                       |

| Accessing           | L   | Н  | L  | Χ  | X                                   | READ/WRIT                     | ILLEGAL                                       |

|                     | L   | L  | Χ  | Х  | Х                                   | ACT/PRE/PALL/<br>REF/SELF/MRS | ILLEGAL                                       |

Remark H = High level, L = Low level, X = High or Low level (Don't care), AP = Auto Pre-charge

Note 7: All entries assume that CKE was active (High level) during the preceding clock cycle.

**Note 8:** If all banks are idle, and CKE is inactive (Low level), SDRAM will enter Power down mode. All input buffers except CKE will be disabled.

**Note 9:** Illegal to bank in specified states; Function may be legal in the bank indicated by Bank Address (BA), depending on the state of that bank.

**Note 10:** If all banks are idle, and CKE is inactive (Low level), SDRAM will enter Self refresh mode. All input buffers except CKE will be disabled.

Note 11: Illegal if tRCD is not satisfied.

Note 12: Illegal if tRAS is not satisfied.

Note 13: Must satisfy burst interrupt condition.

Note 14: Must satisfy bus contention, bus turn around, and/or write recovery requirements.

Note 15: Must mask preceding data which don't satisfy tDPL.

Note 16: Illegal if tRRD is not satisfied.

#### 5. Command Truth Table for CKF

|                                   | CK        | Œ         |        | /D |       |    |         |                                                |  |

|-----------------------------------|-----------|-----------|--------|----|-------|----|---------|------------------------------------------------|--|

| Current State                     | n-1       | n         | /CS    | /R | /C    | /W | Addr.   | Action                                         |  |

|                                   | Н         | Х         | Х      | ~  | ~     | V  | V       | INVALID, CLK(n-1) would exit self              |  |

|                                   | П         | ^         | ۸      | Х  | Χ     | Х  | X       | refresh                                        |  |

|                                   | L         | Н         | Н      | Χ  | Χ     | Χ  | Χ       | Self refresh recovery                          |  |

| Self Refresh                      | L         | Н         | L      | Н  | Н     | Χ  | Χ       | Self refresh recovery                          |  |

| <u> </u>                          | L         | Н         | L      | Н  | L     | Χ  | Χ       | ILLEGAL                                        |  |

| <u> </u>                          | L         | Н         | L      | L  | Χ     | Χ  | Χ       | ILLEGAL                                        |  |

|                                   | L         | L         | Х      | Χ  | Χ     | Χ  | Х       | Maintain self refresh                          |  |

| <u> </u>                          | Н         | Н         | Н      | Χ  | Χ     | Χ  | Χ       | Idle after t <sub>RC</sub>                     |  |

| <u> </u>                          | Н         | Н         | L      | Н  | Н     | Χ  | Χ       | Idle after t <sub>RC</sub>                     |  |

| _                                 | Н         | Н         | L      | Н  | L     | Χ  | Χ       | ILLEGAL                                        |  |

| Self Refresh                      | Н         | Н         | L      | L  | Χ     | Χ  | Χ       | ILLEGAL                                        |  |

| Recovery                          | Н         | L         | Н      | Χ  | Χ     | Χ  | Χ       | ILLEGAL                                        |  |

| _                                 | Н         | L         | L      | Н  | Н     | Χ  | Χ       | ILLEGAL                                        |  |

| _                                 | Н         | L         | L      | Н  | L     | Χ  | Χ       | ILLEGAL                                        |  |

|                                   | Н         | L         | L      | L  | Χ     | Χ  | Х       | ILLEGAL                                        |  |

|                                   | Н         | Χ         | Х      | Χ  | Х     | Х  | Х       | INVALID, CLK(n-1) would exit                   |  |

| Power Down                        | _         |           |        |    | V     |    |         | power down                                     |  |

|                                   | L         | <u>H</u>  | X      | X  | X     | X  | X       | Exit power down → Idle                         |  |

|                                   | L         | L_        | X      | X  | X     | X  | Х       | Maintain power down mode                       |  |

| <u> </u>                          | H<br>H    | H<br>H    | H      | X  | X     | X  |         | Refer to operations in Operative               |  |

| -                                 | Н         | <u>-п</u> | L<br>L | L  | <br>H | X  |         | Command Table                                  |  |

|                                   | Н         | <u>-П</u> | L      | L  | L     | H  | Х       | Refresh                                        |  |

|                                   | H         | <u>''</u> | L      | L  | L     | L  | Op-Code | Refresh                                        |  |

|                                   | <u>''</u> | L         | Н      | X  | X     | X  | Op-Couc | Refer to operations in Operative               |  |

| Both Banks                        | H         | L         | L      | Ĥ  | X     | X  |         | Command Table                                  |  |

| ldle -                            | H         | L         | L      | L  | Н     | X  |         | Command rabio                                  |  |

|                                   | Н         | L         | L      | L  | L     | Н  | Х       | Self refresh (Note 17)                         |  |

|                                   | Н         | L         | L      | L  | L     | L  | Op-Code | Refer to operations in Operative Command Table |  |

|                                   | L         | Χ         | Х      | Χ  | Х     | Х  | Х       | Power down (Note 17)                           |  |

| Row Active                        | Н         | Х         | Х      | Х  | Х     | Х  | Х       | Refer to operations in Operative Command Table |  |

|                                   | L         | Χ         | Х      | Χ  | Х     | Х  | Х       | Power down (Note 17)                           |  |

|                                   | Н         | Н         | Х      | Х  | Х     | Х  |         | Refer to operations in Operative Command Table |  |

| Any State Other than Listed above | Н         | L         | Х      | Χ  | Х     | Х  | Х       | Begin clock suspend next cycle (Note 18)       |  |

|                                   | L         | Н         | Х      | Χ  | Χ     | Х  | Х       | Exit clock suspend next cycle                  |  |

| i F                               | L         | L         | Х      | Χ  | Х     | Χ  | Х       | Maintain clock suspend                         |  |

**Remark:** H = High level, L = Low level, X = High or Low level (Don't care)

Notes 17: Self refresh can be entered only from the both banks idle state.

Power down can be entered only from both banks idle or row active state.

Notes 18: Must be legal command as defined in Operative Command Table

# Package Description

#### Package Outline TFBGA 54 Ball (8x8 mm<sub>2</sub>, ball pitch:0.8mm, Ø =0.45mm)

| SYMBOL   | DIM  | ENSION (m | nm)  | DIMENSION (inch) |            |       |  |

|----------|------|-----------|------|------------------|------------|-------|--|

| STINIBUL | MIN. | NOM.      | MAX. | MIN.             | NOM.       | MAX.  |  |

| Α        |      |           | 1.20 |                  |            | 0.047 |  |

| A1       | 0.28 |           | 0.40 | 0.010            |            | 0.016 |  |

| b        | 0.40 | 0.45      | 0.50 | 0.016            | 0.018      | 0.020 |  |

| D        | 7.90 | 8.00      | 8.10 | 0.311            | 0.315      | 0.319 |  |

| D1       |      | 6.40 BSC. |      | 0.252 BSC.       |            |       |  |

| E        | 7.90 | 8.00      | 8.10 | 0.311            | 0.315      | 0.319 |  |

| E1       |      | 6.40 BSC. |      | 0.252 BSC.       |            |       |  |

| SE       |      | 1.60 TYP. |      | 0.063 TYP.       |            |       |  |

| SD       |      | 0.80 TYP. |      | 0.031 TYP.       |            |       |  |

| е        |      | 0.80 BSC. |      | (                | 0.031 BSC. |       |  |

| CCC      |      |           | 0.10 |                  |            | 0.004 |  |

Note: 1. Ball land : 0.5mm 2. Ball opening : 0.4mm

3. PCB Ball land suggested ≤ 0.4mm

# Revision History

| Revision No. | History              | Draft Date | Editor    | Remark |

|--------------|----------------------|------------|-----------|--------|

| 0.1          | Initial Release.     | Aug. 2016  | Maven Hsu | N/A    |

| 1.0          | First SPEC. release. | Aug. 2016  | Maven Hsu | N/A    |