## 8Gb (32Mx8Banksx32) Low Power DDR4 SDRAM

### **Descriptions**

H2AB08G32E6R uses the double data rate architecture on the Command/Address (CA) bus to reduce the number of input pins in the system. Each command uses one clock cycle, during which command information is transferred on both the positive and negative edge of the clock. To achieve high-speed operation, our H2AB08G32E6R • Programmable READ and WRITE latencies (RL/WL) SDRAM adopt 16n-prefetch interface designed to transfer two data per clock cycle at the I/O pins. A single read or write access for the H2AB08G32E6R effectively consists of a single 8n-bit wide, one clock cycle data transfer at the internal SDRAM core and eight corresponding n-bit wide, one-half-clock-cycle data transfer at the I/O pins. Read and write accesses to the H2AB08G32E6R are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence.

For H2AB08G32E6R devices, accesses begin with the registration of an Active command, which is then followed by a Read or Write command. The address and BA bits registered coincident with the Active command are used to select the row and the Bank to be accessed. The address bits registered coincident with the Read or Write command are used to select the Bank and the starting column location for the burst access.

#### Features

- Frequency to 1600MHz (data rate: 3200Mbps/pin)

- 16n prefetch DDR architecture

- 8 internal banks per channel for concurrent operation

- Single-data-rate CMD/ADR entry

- Bidirectional/differential data strobe per byte lane

- Programmable Burst Lengths: 16,32

- Partial-array self refresh (PASR)

- Selectable output drive strength (DS)

- Clock Stop capability during idle period

- · RoHS-compliant, "green" packaging

- Programmable VSS (ODT) termination

- · Auto Refresh and Self Refresh Modes

- FBGA "green" package 200-ball VFBGA

- Operating temperature range : Single Low: -30°C to 85°C Commercial: 0°C to 85°C

- · Directed per-bank refresh for concurrent bank operation and ease of command scheduling

- VDD1/VDD2/VDDQ= 1.8V/1.1V/1.1V or 0.6V

### **Ordering Information**

| Part No           | Organization | Max. Freq    | Package       | Grade      |

|-------------------|--------------|--------------|---------------|------------|

| H2AB08G32E6RIAAC  | 512M X 32    | LP DDR4-2400 |               | Commercial |

| H2AB08G32E6RKAAC  | 512M X 32    | LP DDR4-3200 | 200Ball       | Commercial |

| H2AB08G32E6RIAASL | 512M X 32    | LP DDR4-2400 | BGA,10x14.5mm | Single Low |

| H2AB08G32E6RKAASL | 512M X 32    | LP DDR4-3200 |               | Single Low |

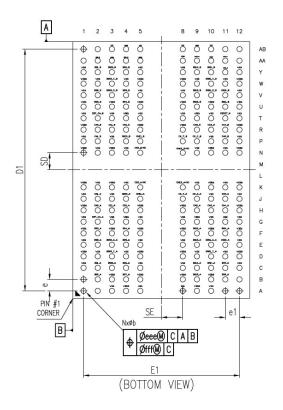

## Pin Assignment

|   | 1                | 2               | 3                | 4                | 5                |

|---|------------------|-----------------|------------------|------------------|------------------|

| Α | DNU              | DNU             | V <sub>SS</sub>  | V <sub>DD2</sub> | ZQ0              |

| В | DNU              | DQ0_A           | V <sub>DDQ</sub> | DQ7_A            | V <sub>DDQ</sub> |

| C | V <sub>SS</sub>  | DQ1_A           | DMI0_A           | DQ6_A            | V <sub>SS</sub>  |

| D | V <sub>DDQ</sub> | V <sub>SS</sub> | DQS0_t_A         | V <sub>SS</sub>  | V <sub>DDQ</sub> |

| Ε | V <sub>SS</sub>  | DQ2_A           | DQS0_c_A         | DQ5_A            | V <sub>SS</sub>  |

| F | V <sub>DD1</sub> | DQ3_A           | V <sub>DDQ</sub> | DQ4_A            | V <sub>DD2</sub> |

| G | V <sub>SS</sub>  | ODT_CA_A        | V <sub>SS</sub>  | V <sub>DD1</sub> | V <sub>SS</sub>  |

| Н | V <sub>DD2</sub> | CA0_A           | NC               | CS0_A            | V <sub>DD2</sub> |

| J | V <sub>SS</sub>  | CA1_A           | V <sub>SS</sub>  | CKE0_A           | NC               |

| K | V <sub>DD2</sub> | V <sub>SS</sub> | V <sub>DD2</sub> | V <sub>SS</sub>  | NC               |

|   |                  |                 |                  |                  |                  |

| 8                | 9                | 10               | 11              | 12.              |

|------------------|------------------|------------------|-----------------|------------------|

| NC               | V <sub>DD2</sub> | V <sub>SS</sub>  | DNU             | DNU              |

| V <sub>DDQ</sub> | DQ15_A           | V <sub>DDQ</sub> | DQ8_A           | DNU              |

| V <sub>SS</sub>  | DQ14_A           | DMI1_A           | DQ9_A           | V <sub>SS</sub>  |

| V <sub>DDQ</sub> | V <sub>SS</sub>  | DQS1_t_A         | V <sub>SS</sub> | V <sub>DDQ</sub> |

| V <sub>SS</sub>  | DQ13_A           | DQS1_c_A         | DQ10_A          | V <sub>SS</sub>  |

| V <sub>DD2</sub> | DQ12_A           | V <sub>DDQ</sub> | DQ11_A          | V <sub>DD1</sub> |

| V <sub>SS</sub>  | V <sub>DD1</sub> | V <sub>SS</sub>  | NC              | V <sub>SS</sub>  |

| V <sub>DD2</sub> | CA2_A            | CA3_A            | CA4_A           | V <sub>DD2</sub> |

| CK_t_A           | CK_c_A           | V <sub>SS</sub>  | CA5_A           | V <sub>SS</sub>  |

| NC               | V <sub>SS</sub>  | V <sub>DD2</sub> | V <sub>SS</sub> | V <sub>DD2</sub> |

|                  |                  |                  |                 |                  |

| Μ  |                  |                 |                  |                  |                  |

|----|------------------|-----------------|------------------|------------------|------------------|

| N  | V <sub>DD2</sub> | V <sub>SS</sub> | V <sub>DD2</sub> | V <sub>SS</sub>  | NC               |

| Р  | V <sub>SS</sub>  | CA1_B           | V <sub>SS</sub>  | CKE0_B           | NC               |

| R  | V <sub>DD2</sub> | CA0_B           | NC               | CS0_B            | V <sub>DD2</sub> |

| Т  | V <sub>SS</sub>  | ODT_CA_B        | V <sub>SS</sub>  | V <sub>DD1</sub> | V <sub>SS</sub>  |

| U  | V <sub>DD1</sub> | DQ3_B           | V <sub>DDQ</sub> | DQ4_B            | V <sub>DD2</sub> |

| ٧  | V <sub>SS</sub>  | DQ2_B           | DQS0_c_B         | DQ5_B            | V <sub>SS</sub>  |

| W  | V <sub>DDQ</sub> | V <sub>SS</sub> | DQS0_t_B         | V <sub>SS</sub>  | V <sub>DDQ</sub> |

| Υ  | V <sub>SS</sub>  | DQ1_B           | DMI0_B           | DQ6_B            | V <sub>SS</sub>  |

| ٩A | DNU              | DQ0_B           | V <sub>DDQ</sub> | DQ7_B            | V <sub>DDQ</sub> |

| AB | DNU              | DNU             | V <sub>SS</sub>  | V <sub>DD2</sub> | V <sub>SS</sub>  |

|    | 1                | 2               | 3                | 4                | 5                |

| NC               | V <sub>SS</sub>  | V <sub>DD2</sub> | V <sub>SS</sub> | V <sub>DD2</sub> |

|------------------|------------------|------------------|-----------------|------------------|

| CK_t_B           | CK_c_B           | V <sub>SS</sub>  | CA5_B           | V <sub>SS</sub>  |

| V <sub>DD2</sub> | CA2_B            | CA3_B            | CA4_B           | V <sub>DD2</sub> |

| V <sub>SS</sub>  | V <sub>DD1</sub> | V <sub>SS</sub>  | RESET_n         | V <sub>SS</sub>  |

| V <sub>DD2</sub> | DQ12_B           | V <sub>DDQ</sub> | DQ11_B          | V <sub>DD1</sub> |

| V <sub>SS</sub>  | DQ13_B           | DQS1_c_B         | DQ10_B          | V <sub>SS</sub>  |

| V <sub>DDQ</sub> | V <sub>SS</sub>  | DQS1_t_B         | V <sub>SS</sub> | V <sub>DDQ</sub> |

| V <sub>SS</sub>  | DQ14_B           | DMI1_B           | DQ9_B           | V <sub>SS</sub>  |

| V <sub>DDQ</sub> | DQ15_B           | V <sub>DDQ</sub> | DQ8_B           | DNU              |

| V <sub>SS</sub>  | V <sub>DD2</sub> | V <sub>SS</sub>  | DNU             | DNU              |

| 8                | 9                | 10               | 11              | 12               |

Top View (ball down)

DDR4\_A (Channel A) DDR4\_B (Channel B) ZQ, ODT\_CA, RESET Supply Ground

#### 200-Ball FBGA

# Pin Description (Simplified)

| Symbol                    | Type   | Description                                                                       |

|---------------------------|--------|-----------------------------------------------------------------------------------|

|                           |        | Clock: CK_t and CK_c are differential clock inputs. All address,                  |

|                           |        | command and control input signals are sampled on positive edge of CK_t            |

| CK_t_A, CK_c_A, CK_t_B,   | Input  | and the negative edge of CK_c. AC                                                 |

| CK_c_B                    | p w/   | timings for CA parameters are referenced to clock. Each channel (A, B)            |

|                           |        | has its own clock pair.                                                           |

|                           |        | Clock enable: CKE HIGH activates and CKE LOW deactivates the                      |

| CKE0_A, CKE0_B            | Input  | internal clock signals, input buffers, and output drivers. Power-saving           |

| CKEU_A, CKEU_B            | IIIput | modes are entered and exited via CKE transitions. CKE is sampled at               |

|                           |        | the rising edge of CK.                                                            |

| CS0_A, CS0_B              | Input  | Chip select: Each channel (A, B) has its own CS signals.                          |

|                           |        | Command/address inputs: Provide the command and address inputs                    |

| CA[5:0]_A, CA[5:0]_B      | Input  | according to the command truth table. Each channel (A, B) has its own             |

| CA[J.0]_A, CA[J.0]_B      | Input  | CA signals.                                                                       |

|                           |        | CA ODT Control: The ODT_CA pin is used in conjunction with the                    |

|                           |        | mode register to turn on/off the on-die termination for CA pins. It is            |

| ODT_CA_A, ODT_CA_B        | Toward | bonded to $V_{\text{DD2}}$ within the package, or at the package ball, for the    |

| ODI_CA_A, ODI_CA_B        | Input  | terminating rank, and the non-terminating ranks are bonded to $V_{\text{SS}}$ (or |

|                           |        | left floating with a weak pull-down on the DRAM die). The terminating             |

|                           |        | rank is the DRAM that terminates the CA bus for all die on the same               |

|                           |        | channel.                                                                          |

| DQ[15:0]_A, DQ[15:0]_B    | I/O    | Data input/output: Bidirectional data bus.                                        |

|                           |        | Data strobe: DQS_t and DQS_c are bi-directional differential output               |

|                           |        | clock signals used to strobe data during a READ or WRITE. The data                |

| DQS[1:0]_t_A,DQS[1:0]_c_  |        | strobe is generated by the DRAM for a READ and is edge-aligned with               |

| A,                        |        | data. The data strobe is generated by the SoC memory controller for a             |

| DQS[1:0]_t_B,DQS[1:0]_c_B |        | WRITE and is trained to precede data. Each byte of data has a data strobe         |

| DQS[1.0]_C_D,DQS[1.0]_C_D |        | signal pair. Each channel (A, B) has its own DQS_t and DQS_c                      |

|                           |        | strobes.                                                                          |

|                             |           | Data Mask/Data Bus Inversion: DMI is a dual use bi-directional signal                                                                        |

|-----------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|

|                             |           | used to indicate data to be masked, and data which is inverted on the bus.                                                                   |

|                             |           | For data bus inversion                                                                                                                       |

|                             |           | (DBI), the DMI signal is driven HIGH when the data on the data bus is                                                                        |

| DMI(1.0) A DMI(1.0) D       | 1/0       | inverted, or driven LOW when the data is in its normal state. DBI can be                                                                     |

| DMI[1:0]_A,DMI[1:0]_B       | I/O       | disabled via a mode register setting. For data mask, the DMI signal is                                                                       |

|                             |           | used in combination with the data lines to indicate data to be masked in a                                                                   |

|                             |           | MASK WRITE command (see the Data Mask (DM) and Data Bus                                                                                      |

|                             |           | Inversion (DBI) sections for details). The data mask function can be                                                                         |

|                             |           | disabled via a mode register setting. Each byte of data has a DMI                                                                            |

|                             |           | signal. Each channel has its Own DMI signals.                                                                                                |

|                             |           | ZQ Calibration Reference: Used to calibrate the output drive strength                                                                        |

| ZQ0                         | Reference | and the termination resistance. There is one ZQ pin per die. The ZQ pin shall be connected to $V_{DDQ}$ through a 240 $\Omega$ ±1% resistor. |

| $V_{DDQ}, V_{DD1}, V_{DD2}$ | Supply    | Power supplies: Isolated on the die for improved noise immunity.                                                                             |

| $ m V_{SS}$                 | Supply    | Ground Reference: Power supply ground reference.                                                                                             |

| RESET_n                     | Input     | RESET: When asserted LOW, the RESET pin resets both channels of                                                                              |

| KLSL1_II                    | Input     | the die.                                                                                                                                     |

| DNU                         | -         | Do not use: Must be grounded or left floating.                                                                                               |

| NC                          | -         | No connect: Not internally connected.                                                                                                        |

# SDRAM Addressing

|                   |                                    |                     | 256M32 (8Gb/Package)   |  |

|-------------------|------------------------------------|---------------------|------------------------|--|

| Die Configuration | Channel A, Rank                    | 0                   | x16 mode x 1 die       |  |

|                   | Channel B, Rank                    | 0                   | x16 mode x 1 die       |  |

| Die Addressing    | Device density (p                  | per die)            | 4Gb                    |  |

|                   | Device density (p                  | per channel)        | 4Gb                    |  |

|                   | Configuration(p                    | er die)             | 32Mb x 16 DQ x 8 Banks |  |

|                   | Number of cha                      | nnels (per die)     | 1                      |  |

|                   | Number of ban                      | ks (per channel)    | 8                      |  |

|                   | Array prefetch                     | (bits, per channel) | 256                    |  |

|                   | Number of rows                     | s (per channel)     | 32,768                 |  |

|                   | Number of columboundaries)         | umns (fetch         | 64                     |  |

|                   | Page size (bytes)                  |                     | 2048                   |  |

|                   | Channel density (bits per channel) |                     | 4,294,967,296          |  |

|                   | Total density (b                   | its per die)        | 4,294,967,296          |  |

|                   | Bank address                       | T                   | BA[2:0]                |  |

|                   |                                    | Row address         | R[14:0]                |  |

|                   | x16 Column address                 |                     | C[9:0]                 |  |

|                   | Burst starting address boundary    |                     | 64-bit                 |  |

### Absolute Maximum Rating

| Symbol            | Item                                | Rating     | Units |

|-------------------|-------------------------------------|------------|-------|

| $V_{IN}, V_{OUT}$ | Voltage on any ball relative to VSS | -0.4 ~ 1.5 | V     |

| V <sub>DD1</sub>  | VDD1 supply voltage relative to VSS | -0.4 ~ 2.1 | V     |

| $V_{DD2}$         | VDD2 supply voltage relative to VSS | -0.4 ~ 1.5 | V     |

| $V_{DDQ}$         | VDDQ supply voltage relative to VSS | -0.4 ~ 1.5 | V     |

| T <sub>STG</sub>  | Storage Temperature (plastic)       | -55 ~ 125  | °C    |

- **Note 1:** For information about relationships between power supplies, see the Voltage Ramp and Device Initialization section.

- **Note 2:** Storage temperature is the case surface temperature on the center/top side of the device. For measurement conditions, refer to the JESD51-2 standard.

### Input / Output Capacitance

| Symbol            | Parameter                                          | Min. | Max. | Units |

|-------------------|----------------------------------------------------|------|------|-------|

| C <sub>CK</sub>   | Input capacitance, CK_t and CK_c                   | 0.5  | 0.9  | pF    |

| C <sub>DCK</sub>  | Input capacitance delta, CK_t and CK_c             | 0    | 0.09 | pF    |

| Cı                | I Input capacitance, all other input-only pins     | 0.5  | 0.9  | pF    |

| C <sub>DI</sub>   | Input capacitance delta, all other input-only pins | -0.1 | 0.1  | pF    |

| C <sub>IO</sub>   | Input/output capacitance, DQ, DMI, DQS_t, DQS_c    | 0.7  | 1.3  | pF    |

| C <sub>DDQS</sub> | Input/output capacitance delta, DQS_t, DQS_c       | 0    | 0.1  | pF    |

| C <sub>DIO</sub>  | Input/output capacitance delta, DQ, DMI            | -0.1 | 0.1  | pF    |

| C <sub>ZQ</sub>   | Input/output capacitance, ZQ pin                   | 0    | 5.0  | pF    |

- **Note 1:** This parameter is not subject to production testing. It is verified by design and characterization.

- Note 2: This parameter is not subject to production test. It is verified. The capacitance is measured according to JEP147 (Procedure for measuring input capacitance using a vector network analyzer (VNA) with VDD1, VDD2, VDDQ, VSS, VSS, VSS applied and all other pins floating.

- Note 3: Absolute value of CKCK\_t CKCK\_c

- Note 4: CI applies to CS, CKE and CA[5:0].

- **Note 5:** CDI = CI  $-0.5 \times (CCK_t + CKCK_c)$ ; it does not apply to CKE.

- Note 6: DMI loading matches DQ and DQS.

- **Note 7:** MR3 I/O configuration DS OP3-OP0 = 0001B (34.3 $\Omega$ typical).

- Note 8: Absolute value of CDQS\_t and CDQS\_c.

- Note 9: CDIO = CIO Average(CDQn, CDMI, CDQS\_t, CDQS\_c) in byte-lane

### Recommended DC Operating Conditions

| Symbol    | Parameter             | Min.      | Тур.    | Max.      | Units |

|-----------|-----------------------|-----------|---------|-----------|-------|

| $V_{DD1}$ | Core Supply voltage 1 | 1.70      | 1.80    | 1.95      | V     |

| $V_{DD2}$ | Core Supply voltage 2 | 1.06      | 1.10    | 1.17      | V     |

| $V_{DDQ}$ | I/O buffer power      | 0.57/1.06 | 0.6/1.1 | 0.65/1.17 | V     |

- Notes: 1. VDD1 uses significantly less power than VDD2.

- **Notes: 2.** The voltage range is for DC voltage only. DC voltage is the voltage supplied at the DRAM and is inclusive of all noise up to 20 MHz at the DRAM package ball.

- **Notes: 3.** The voltage noise tolerance from DC to 20 MHz exceeding a peak-to-peak tolerance of 45mV at the DRAM ball is not included in the TdIVW.

# IDD Specification Parameters and Operating Conditions

| Parameter/Condition                                                                   | Symbol  | Power<br>Supply | Current | Notes |

|---------------------------------------------------------------------------------------|---------|-----------------|---------|-------|

| Operating one bank active-precharge current:                                          | IDD01   | VDD1            | TBD     |       |

| tCK=tCK(MIN);tRC=tRC(MIN); CKE is HIGH; CS is                                         |         |                 | TBD     |       |

| LOW between valid commands;CA bus inputs are                                          | IDD02   | VDD2            |         |       |

| switching; Data bus inputs are stable;ODT is disabled                                 | IDD0Q   | VDDQ            | TBD     |       |

| Idle power-down standby current:tCK = tCK (MIN); CKE is                               | IDD2P1  | VDD1            | TBD     |       |

| LOW; CS is LOW; All banks are idle; CA bus inputs are                                 | IDD2P2  | VDD2            | TBD     |       |

| switching;Data bus inputs are stable; ODT is disabled                                 | IDD2PQ  | VDDQ            | TBD     |       |

| Idle power-down standby current with clock stop: CK_t                                 | IDD2PS1 | VDD1            | TBD     |       |

| =LOW, CK_c = HIGH; CKE is LOW; CS is LOW; All                                         | IDD2PS2 | VDD2            | TBD     |       |

| banks are idle; CA bus inputs are stable; Data bus inputs are stable; ODT is disabled | IDD2PSQ | VDDQ            | TBD     |       |

| Parameter/Condition                                                                                                | Symbol  | Power<br>Supply | Current | Notes |

|--------------------------------------------------------------------------------------------------------------------|---------|-----------------|---------|-------|

| Idle non-power-down standby current: tCK = tCK (MIN);                                                              | IDD2N1  | VDD1            | TBD     |       |

| CKE is HIGH; CS is LOW; All banks are idle; CA bus inputs                                                          | IDD2N2  | VDD2            | TBD     |       |

| are switching;Data bus inputs are stable; ODT is disabled                                                          | IDD2NQ  | VDDQ            | TBD     |       |

| Idle non-power-down standby current with clock                                                                     | IDD2NS1 | VDD1            | TBD     |       |

| stopped:CK_t = LOW; CK_c = HIGH; CKE is HIGH; CS is                                                                | IDD2NS2 | VDD2            | TBD     |       |

| LOW; All banks are idle; CA bus inputs are stable; Data bus                                                        | IDD2NSQ | VDDQ            | TBD     |       |

| inputs are stable; ODT is disabled                                                                                 |         |                 |         |       |

| Active power-down standby current: tCK = tCK (MIN);                                                                | IDD3P1  | VDD1            | TBD     |       |

| CKE is LOW; CS is LOW; One bank is active; CA bus                                                                  | IDD3P2  | VDD2            | TBD     |       |

| inputs are switching;Data bus inputs are stable; ODT is                                                            | IDD3PQ  | VDDQ            | TBD     |       |

| disabled                                                                                                           |         |                 |         |       |

| Active power-down standby current with clock stop: CK_t =                                                          | IDD3PS1 | VDD1            | TBD     |       |

| LOW, CK_c = HIGH; CKE is LOW; CS is LOW; One bank is active; CA bus inputs are stable; Data bus inputs are stable; | IDD3PS2 | VDD2            | TBD     |       |

| ODT is disabled                                                                                                    | IDD3PSQ | VDDQ            | TBD     |       |

|                                                                                                               |         |      |     | <u> </u> |

|---------------------------------------------------------------------------------------------------------------|---------|------|-----|----------|

| Active non-power-down standby current: tCK = tCK                                                              | IDD3N1  | VDD1 | TBD |          |

| (MIN);CKE is HIGH; CS is LOW; One bank is active; CA                                                          | IDD3N2  | VDD2 | TBD |          |

| bus inputs are switching; Data bus inputs are stable; ODT is                                                  | IDD3NQ  | VDDQ | TBD |          |

| disabled                                                                                                      |         |      |     |          |

| Active non-power-down standby current with clock stopped:                                                     | IDD3NS1 | VDD1 | TBD |          |

| $CK_t = LOW$ , $CK_c = HIGH$ ; $CKE$ is $HIGH$ ; $CS$ is $LOW$ ;                                              | IDD3NS2 | VDD2 | TBD |          |

| One bank is active; CA bus inputs are stable; Data bus inputs                                                 | IDD3NSQ | VDDQ | TBD |          |

| are stable; ODT is disabled                                                                                   |         |      |     |          |

| Operating burst READ current: tCK = tCK (MIN); CS is                                                          | IDD4R1  | VDD1 | TBD |          |

| LOW between                                                                                                   | IDD4K1  | VDDI |     |          |

| valid commands; One bank is active; BL = 16 or 32; RL =                                                       | IDD4R2  | VDD2 | TBD |          |

| RL(MIN);                                                                                                      |         |      | TBD |          |

| CA bus inputs are switching; 50% data change each                                                             | IDD4RQ  | VDDQ | ТЫ  | 2,3      |

| bursttransfer;                                                                                                |         |      |     |          |

| ODT is disabled                                                                                               |         |      |     |          |

| Operating burst WRITE current: tCK = tCK (MIN); CS is                                                         | IDD4W1  | VDD1 | TBD |          |

| LOW between                                                                                                   | IDD4W2  | VDD2 | TBD |          |

| valid commands; One bank is active; BL = 16 or 32; WL = WL(MIN); CA bus inputs are switching; 50% data change | IDD4WQ  | VDDQ | TBD | 3        |

| each burst transfer; ODT is disabled                                                                          |         | ,    |     |          |

| Parameter/Condition                                         | Symbol  | Power<br>Supply | Current | Notes |

|-------------------------------------------------------------|---------|-----------------|---------|-------|

| All-bank REFRESH burst current: tCK = tCK (MIN); CKE        | IDD51   | VDD1            | TBD     |       |

| is HIGHbetween valid commands; tRC = tRFCab (MIN);          | IDD52   | VDD2            | TBD     |       |

| Burst refresh; CA bus inputs are switching; Data bus inputs | IDD5Q   | VDDQ            | TBD     |       |

| are stable; ODT is disabled                                 |         |                 |         |       |

| All-bank REFRESH average current: tCK = tCK (MIN);          | IDD5AB1 | VDD1            | TBD     |       |

| CKE is High between valid commands tRC = tREFI; CA bus      | IDD5AB2 | VDD2            | TBD     |       |

| inputs are switching; Data bus inputs are stable; ODT is    | IDD5ABQ | VDDQ            | TBD     |       |

| disabled                                                    |         |                 |         |       |

| Per-bank REFRESH average current: tCK = tCK (MIN);          | IDD5PB1 | VDD1            | TBD     |       |

| CKE is High between valid commands tRC = tREFI; CA bus      | IDD5PB2 | VDD2            | TBD     |       |

| inputs are switching; Data bus inputs are stable; ODT is | IDD5PBQ | VDDQ | TBD |  |

|----------------------------------------------------------|---------|------|-----|--|

| disabled                                                 |         |      |     |  |

| Power-down self refresh current: CK_t = LOW, CK_c =      | IDD61   | VDD1 | TBD |  |

| HIGH;CKE is LOW; CA bus inputs are stable; Data bus      | IDD62   | VDD2 | TBD |  |

| inputs are stable;Maximum 1x self refresh rate; ODT is   | IDD6Q   | VDDQ | TBD |  |

| disabled(25℃)                                            |         |      |     |  |

#### Notes:

- 1.Published IDD values except IDD4RQ are the maximum of the distribution of the arithmeticmean. Refer to the following note for IDD4RQ;

- 2.IDD4RQ value is reference only. Typical value. DBI disabled, VOH = VDDQ/3, TC = 25°C.

- 3.Measurement conditions of IDD4R and IDD4W values: DBI disabled, BL = 16.

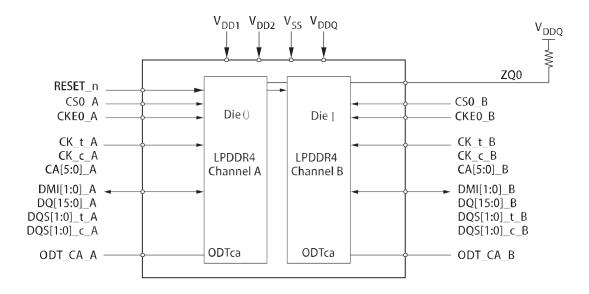

## Package Block Diagram - Dual-Die, Dual-Channel, Single Rank

#### Note:

1. ODT\_CA for Rank 0 of each channel is wired to the respective ODT ball. DT\_CA for Rank 1 of each channel is wired to VSS in the package.

## Initialization Timing Parameters

| Parameter | Min. | Max. | Unit | Comment                                                   |  |  |  |

|-----------|------|------|------|-----------------------------------------------------------|--|--|--|

| tINIT0    | 1    | 20   | ms   | Maximum voltage ramp time                                 |  |  |  |

| tlNIT1    | 200  | -    | us   | Minimum RESET_n LOW time after completion of voltage ramp |  |  |  |

| tlNIT2    | 10   | 1    | ns   | Minimum CKE LOW time before RESET_n goes HIGH             |  |  |  |

| tINIT3    | 2    | -    | ms   | Minimum CKE LOW time after RESET_n goes HIGH              |  |  |  |

| tlNIT4    | 5    | -    | tCK  | Minimum stable clock before first CKE HIGH                |  |  |  |

| tINIT5    | 2    | 1    | us   | Minimum idle time before first MRW/MRR command            |  |  |  |

| tCKb      | Note | 1, 2 | ns   | Clock cycle time during boot                              |  |  |  |

Notes: 1. Minimum tCKb guaranteed by DRAM test is 18ns.

**Notes: 2.** The system may boot at a higher frequency than dictated by minimum tCKb. The higher boot frequency is system dependent.

#### **AC Characteristics**

## **Clock Timing**

|                               |                       |      | Data Rate |           |      |                      |

|-------------------------------|-----------------------|------|-----------|-----------|------|----------------------|

| Danamatan                     | Complete              | Min/ | 1600      | 2400      | 3200 | Unit                 |

| Parameter                     | Symbol                | Max  | Mbps      | Mbps      | Mbps | Unit                 |

|                               |                       | Min  | 1250      | 833       | 625  | ps                   |

| Average clock period          | <sup>t</sup> CK(avg)  | Max  |           | 100       |      | ns                   |

| Average HIGH pulse            |                       | Min  |           | 0.46      |      |                      |

| width                         | <sup>t</sup> CH(avg)  | Max  |           | 0.54      |      | <sup>t</sup> CK(avg) |

|                               |                       | Min  |           | 0.46      |      |                      |

| Average LOW pulse width       | <sup>t</sup> CL(avg)  | Max  |           | 0.54      |      | <sup>t</sup> CK(avg) |

|                               |                       |      | tCl       | ۲(avg)miı | า +  |                      |

| Absolute clock period         | tCK(abs)              | Min  | tJ        | IIT(per)m | in   | ps                   |

| Absolute clock HIGH           |                       | Min  | 0.43      |           |      |                      |

| pulse width                   | <sup>t</sup> CH(abs)  | Max  |           | 0.57      |      | <sup>t</sup> CK(avg) |

| Absolute clock LOW pulse      |                       | Min  |           | 0.43      |      |                      |

| width                         | tCL(abs)              | Max  |           | 0.57      |      | <sup>t</sup> CK(avg) |

|                               | <sup>t</sup> JIT(per) | Min  | -70       | TBD       | -40  |                      |

| Clock period jitter           | allowed               | Max  | 70        | TBD       | 40   | ps                   |

| Maximum clock jitter          |                       |      |           |           |      |                      |

| between two                   | <sup>t</sup> JIT(cc)  | max  | 140       | TBD       | 80   | ps                   |

| consecutiveclock cycles       | allowed               |      |           |           |      | I                    |

| (includes clockperiod jitter) |                       |      |           |           |      |                      |

# Read Output Timing

|                                                                     |                                  |      | Data Rate               |        |           |       |       |

|---------------------------------------------------------------------|----------------------------------|------|-------------------------|--------|-----------|-------|-------|

|                                                                     |                                  | Min/ | 1600                    | 240    | 3200      |       |       |

| Parameter                                                           | Symbol                           | Max  | Mbps                    | Mb     | ps Mbps   | Unit  | Notes |

| DQS output access time from                                         |                                  | Min  |                         | 1500   | )         | -     |       |

| CK_t/CK_c                                                           | ¹DQSCK                           | Max  |                         | 3500   | )         | ps    | 6,11  |

| DQS output access time from CK_t/CK_c –voltage variation            | 'DQSCK_<br>VOLT                  | Max  |                         | 7      |           | ps/mV | 6     |

| DQS output access time from CK_t/CK_c- temperature variation        | ¹DQSCK_<br>TEMP                  | Max  |                         | 4      |           | ps°/C | 6     |

| CK to DQS rank to rank variation                                    | <sup>t</sup> DQSCK_ran<br>k2rank | Max  |                         | 1.0    |           | ns    | 6,11  |

| DQS_t, DQS_c to DQ skew total, per group, per access (DBI Disabled) | 'DQSQ                            | Max  | 0.18                    |        |           | UI    | 9,11  |

| DQ output hold time total from DQS_t, DQS_c (DBI Disabled)          | tQH                              | Min  |                         | MIN(tQ | SH, tQSL) | ps    | 10,11 |

| Data output valid window time total, per pin (DBI-Disabled)         | <sup>t</sup> QW_total            | Min  | 0.75                    | 0.73   | 0.7       | UI    | 9,11  |

| DQS_t, DQS_c to DQ skew total, per group, per access (DBI-Enabled)  | 'DQSQ_<br>DBI                    | Max  | 0.18                    |        | UI        | 10,11 |       |

| DQ output hold time total from DQS_t, DQS_c (DBI-Enabled)           | 'QH_DBI                          | Min  | MIN('QSH_DBI, 'QSL_DBI) |        |           | ps    |       |

|                                                            | I                   |      | ПИВОВОЗИ                                                           |                                                                                         |                                       |                      |       |

|------------------------------------------------------------|---------------------|------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------|----------------------|-------|

|                                                            |                     |      |                                                                    | D                                                                                       | ata Rate                              |                      |       |

|                                                            |                     | Min/ | 1600                                                               | 2400                                                                                    | 3200                                  |                      |       |

| Parameter                                                  | Symbol              | Max  | Mbps                                                               | Mbps                                                                                    | Mbps                                  | Unit                 | Notes |

| Data output valid window time total, per pin (DBI-Enabled) | 'QW_total<br>_DBI   | Min  | 0.75                                                               | 0.73                                                                                    | 0.7                                   | UI                   |       |

| DQS_t, DQS_c differential output LOW time (DBI-Disabled)   | 'QSL                | Min  |                                                                    | <sup>t</sup> CL(a                                                                       | bs) – 0.05                            | <sup>t</sup> CK(avg) |       |

| DQS_t, DQS_c differential output HIGH time (DBI-Disabled)  | 'QSH                | Min  |                                                                    | ¹CH(a                                                                                   | bs) – 0.05                            | <sup>t</sup> CK(avg) |       |

| DQS_t, DQS_c differential output LOW time (DBI-Enabled)    | 'QSL-DBI            | Min  |                                                                    | <sup>t</sup> CL(abs) – 0.045                                                            |                                       |                      |       |

| DQS_t, DQS_c differential output HIGH time (DBI-Enabled)   | ¹QSH-DBI            | Min  |                                                                    | ¹CH(ab                                                                                  | s) – 0.045                            | ¹CK(avg)             |       |

| Read preamble                                              | <sup>t</sup> RPRE   | Min  |                                                                    | 1.8                                                                                     |                                       | tCK(avg)             |       |

| Read postamble                                             | <sup>t</sup> RPST   | Min  | 0.4                                                                |                                                                                         | atra postamble is                     | tCK(avg)             |       |

| DQS Low-Z from clock                                       | ¹LZ(DQS)            | Min  | ·                                                                  |                                                                                         | QSCK(Min)-<br><sup>1</sup> CK) -200ps | ps                   |       |

| DQ Low-Z from clock                                        | <sup>t</sup> LZ(DQ) | Min  | (RL x <sup>t</sup> C                                               | (RL x 'CK) +'DQSCK(Min) - 200ps                                                         |                                       | ps                   |       |

| DQS High-Z from clock                                      | ¹HZ(DQS)            | Min  | (RL x 'CK) +  'DQSCK(Max)+(BL/2 x 'CK) +  ('RPST(Max)xtCK) - 100ps |                                                                                         |                                       | ps                   |       |

| DQ High-Z from clock                                       | 'HZ(DQ)             | Min  |                                                                    | ('RPST(Max)xtCK) - 100ps  (RL x 'CK) + 'DQSCK(Max) +  'DQSQ(Max) + (BL/2 x  tCK) -100ps |                                       |                      |       |

#### Note:

- 1. This parameter includes DRAM process, voltage, and temperature variation. It also includes the AC noise impact for frequencies >20 MHz and a max voltage of 45mV peakto- peak from DC-20 MHz at a fixed temperature on the package. The voltage supply noise must comply with the component MIN/MAX DC operating conditions.

- tDQSCK\_volt max delay variation as a function of DC voltage variation for VDDQ and VDD2. The voltage supply noise must comply with the component MIN/MAX DC operating conditions. The voltage variation is defined as the max[abs(tDQSCK(MIN)@V1- tDQSCK(MAX)@V2), ABS(tDQSCK(MAX)@V1-tDQSCK(MIN)@V2)]/ABS(V1-V2).

- 3. tDQSCK\_temp MAX delay variation as a function of temperature.

- 4. The same voltage and temperature are applied to tDQSCK\_rank2rank.

- 5. tDQSCK\_rank2rank parameter is applied to multi-ranks per byte lane within a package consisting of the same design dies.

- 6. DQ-to-DQS differential jitter where the total includes the sum of deterministic and random timing terms for a specified BER.

- 7. The deterministic component of the total timing.

- 8. This parameter will be characterized and guaranteed by design.

- 9. tQSL describes the instantaneous differential output low pulse width on DQS\_t DQS\_c, as measured from one falling edge to the next consecutive rising edge.

- 10. tQSH describes the instantaneous differential output high pulse width on DQS\_t DQS\_c, as measured from one falling edge to the next consecutive rising edge.

- 11. This parameter is a function of input clock jitter. These values assume MIN tCH(ABS) and tCL(ABS). When the input clock jitter MIN tCH(ABS) and tCL(ABS) is 0.44 or greater than tCK(AVG), the MIN value of tQSL will be tCL(ABS) 0.04 and tQSH will be tCH(ABS) 0.04.

### Write Timing

Note UI = tCK(AVG)(MIN)/2

|                           |                     |          | [    | Data Rate | )    |      |       |

|---------------------------|---------------------|----------|------|-----------|------|------|-------|

|                           |                     | Min/ Max | 1600 | 2400      | 3200 |      |       |

| Parameter                 | Symbol              |          | Mbps | Mbps      | Mbps | Unit | Notes |

| Rx timing window total at |                     |          |      |           |      |      |       |

| VdIVW voltage levels      | TdIVW_              |          |      |           |      |      |       |

|                           | total               | Max      | 0.   | 22        | 0.25 | UI   | 1,2,3 |

| DQ and DMI input pulse    | TdIPW               | Min      |      | 0.45      |      | UI   | 7     |

| width (at Vcent_dQ)       |                     |          |      |           |      |      |       |

| DQ-to-DQS offset          |                     | Min      |      | 200       |      |      |       |

|                           | <sup>t</sup> DQS2DQ | Max      |      | 800       |      | ps   | 6     |

| DQ-to-DQ offset           | <sup>t</sup> DQDQ   | Max      |      | 30        |      | ps   | 7     |

| DQ-to-DQS offset                   | tDQS2DQ           | Max | 0.6  | ps/°C     | 8     |

|------------------------------------|-------------------|-----|------|-----------|-------|

| emperature variation               | _temp             |     |      |           |       |

| DQ-to-DQS offset voltage           | +D003D0           |     |      |           |       |

| variation                          | tDQS2DQ<br>_volt  | Max | 33   | ps/50 mV  | 9     |

| DQ-to-DQS offset rank to           | tDQS2DQ_          |     |      |           |       |

| rank variation                     | rank2ra nk        | Max | 200  | ps        | 10,11 |

| WRITE command to first DQS         |                   | Min | 0.75 |           |       |

| transition                         | <sup>t</sup> DQSS | Max | 1.25 | tCK(av g) |       |

| DQS input HIGH-level width         | <sup>t</sup> DQSH | -   | 0.4  | tCK(avg)  |       |

| DQS input LOW-level width          | <sup>t</sup> DQSL | Min | 0.4  | tCK(avg)  |       |

| DQS falling edge to CK setup       | <sup>t</sup> DSS  | Min | 0.2  | tCK(avg)  |       |

| DQS falling edge from CK hold time | <sup>t</sup> DSH  | Min | 0.2  | tCK(avg)  |       |

| Write postamble                    | <sup>t</sup> WPST | Min | 0.4  | tCK(av g) |       |

| Write preamble                     | <sup>t</sup> WPRE | Min | 1.8  | tCK(avg)  |       |

#### Note:

- 1. Data Rx mask voltage and timing parameters are applied per pin and include the DRAM DQ-to-DQS voltage AC noise impact for frequencies >20 MHz with a maximum voltage of 45mV peak-to-peak at a fixed temperature on the package. The voltage supply noise must comply to the component MIN/MAX DC operating conditions.

- 2. Rx differential DQ-to-DQS jitter total timing window at the VdIVW voltage levels.

- 3. Defined over the DQ internal VREF range. The Rx mask at the pin must be within the internal VREF(DQ) range irrespective of the input signal common mode.

- 4. Rx mask defined for one pin toggling with other DQ signals in a steady state.

- 5. DQ-only minimum input pulse width defined at the VCENT\_DQ(pin\_mid).

- 6. DQ-to-DQS offset is within byte from DRAM pin to DRAM internal latch. Includes all DRAM process, voltage, and temperature variations.

- 7. DQ-to-DQ offset defined within byte from DRAM pin to DRAM internal latch for a given component.

- 8. tDQS2DQ (MAX) delay variation as a function of temperature.

- 9. tDQS2DQ (MAX) delay variation as a function of the DC voltage variation for VDDQ and VDD2. It includes the VDDQ and VDD2 AC noise impact for frequencies >20 MHz and MAX voltage of 45mV peak-to-peak from DC-20 MHz at a fixed temperature on the package.

- 10. The same voltage and temperature are applied to tDQS2DQ rank2rank.

- 11. tDQS2DQ\_rank2rank parameter is applied to multi-ranks per byte lane within a package consisting of the same design dies.

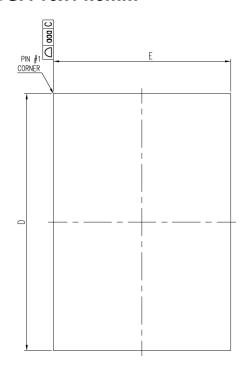

## Package Description

#### 200-ball FBGA 10x14.5mm

| CVALDO | DIMENSION IN MM DIMENSIO |         |                            | ISION    | N IN  | INCH    |       |

|--------|--------------------------|---------|----------------------------|----------|-------|---------|-------|

| SYMBOL | MIN.                     | NOM.    | MAX.                       | MIN.     | NC    | M.      | MAX.  |

| Α      | 0.86                     | 0.93    | 1.00                       | 0.034    | 0.0   | 37      | 0.039 |

| A1     |                          | 0.21    |                            |          | 0.0   | 800     |       |

| A2     | 0.66                     | 0.72    | 0.78                       | 0.026    | 0.0   | 28      | 0.031 |

| р      | 0.25                     | 0.30    | 0.35                       | 0.010    | 0.0   | 12      | 0.014 |

| D      | 14.40                    | 14.50   | 14.60                      | 0.567    | 0.5   | 571     | 0.575 |

| E      | 9.90                     | 10.00   | 10.10                      | 0.390    | 0.394 |         | 0.398 |

| е      | C                        | .65 BS0 | ).                         | 0.       | .026  | BS      | С.    |

| e1     | C                        | .80 BS0 | D.                         | 0.       | .031  | BS      | С.    |

| JEDEC  |                          | N       | 10-311(                    | REF.)/MI | M     |         |       |

| aaa    |                          |         | 0.                         | 10       |       |         |       |

| bbb    |                          |         | 0.                         | 10       |       |         |       |

| ddd    |                          |         | 0.                         | 08       |       |         |       |

| eee    | 0.15                     |         |                            |          |       |         |       |

| fff    |                          | 0.08    |                            |          |       |         |       |

| N      | SE (mr                   | n) SI   | ) (mm)                     | E1 (mr   | n)    | D1      | (mm)  |

| 200    | 1.20 BS                  | SC. 0.9 | 0.975 BSC. 8.80 BSC. 13.65 |          |       | 65 BSC. |       |

# Revision History

| Revision No. | History              | Draft Date | Editor    | Remark |

|--------------|----------------------|------------|-----------|--------|

| 0.1          | Initial Release.     | Feb. 2020  | Rico Yang | N/A    |

| 1.0          | First SPEC. release. | May. 2020  | Rico Yang | N/A    |