# 64Mb (512Kx4Banksx32) Synchronous SDRAM

#### Descriptions

The H2A164M3233N is Synchronous Dynamic Random Access Memory (SDRAM) organized as 512K words x 4 banks by 32 bits. All inputs and outputs are synchronized with the positive edge of the clock.

Accesses to the SDRAM are burst oriented. Consecutive memory location in one page can be accessed at a burst length of 1, 2, 4, 8 or full page when a bank and row is selected by an ACTIVE command. Column addresses are automatically generated by the SDRAM internal counter in burst operation. Random column read is also possible by providing its address at each clock cycle. The multiple bank nature enables interleaving among internal banks to hide the precharging time.

#### Features

- 512K Words × 4 banks × 32 bits organization

- Single 3.3V±0.3V Power Supply

- Self Refresh Mode

- CAS Latency: 2 and 3

- Burst Length: 1, 2, 4, 8 and full page

- Burst Read, Single Writes Mode

- Byte Data Controlled by DQM

- Auto-precharge and Controlled Precharge

- 4K Refresh cycles / 64 mS

- Interface: LVTTL

- Packaged in TSOP II 86 pin, 400x875 mil

- Pb and Halogen Free

# **Ordering Information**

| Part No         | Organization | Max. Freq         | Package        | Grade      |

|-----------------|--------------|-------------------|----------------|------------|

| H2A164M3233NM1C | 2M X 32      | PC-166MHz (3-3-3) | 86pin TSOP(II) | Commercial |

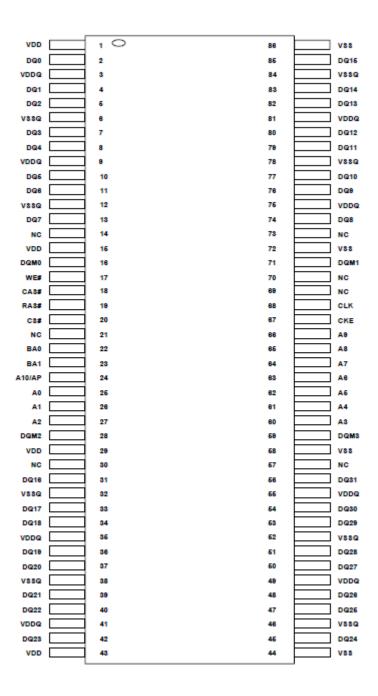

#### Pin Assignment

# Pin Description (Simplified)

| Pin                                                                                                            | Name     | Function                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25-27, 60-66, 24,                                                                                              | A0-A10   | <b>(Address)</b><br>Multiplexed pins for row and column address. Row address:<br>A0–A10. Column address: A0–A7. A10 is sampled during a<br>precharge command to determine if all banks are to be<br>precharged or bank selected by BS0, BS1. |

| 22, 23                                                                                                         | BA0, BA1 | (Bank Select)<br>Select bank to activate during row address latch time, or<br>bank to read/write during address latch time.                                                                                                                  |

| 2,4,5,7,8,10,11,<br>13,74,76,77,79,<br>80,82,83,85,31,<br>33,34,36,37,39,<br>40,42,45,47,48,<br>50,51,53,54,56 | DQ0-DQ31 | <b>(Data Input/ Output)</b><br>Multiplexed pins for data input and output.                                                                                                                                                                   |

| 20                                                                                                             | /CS      | (Chip Select)<br>Disable or enable the command decoder. When command<br>decoder is disabled, new command is ignored and previous<br>operation continues.                                                                                     |

| 19                                                                                                             | /RAS     | (Row Address Strobe)<br>Command input. When sampled at the rising edge of the clock,<br>/RAS, /CAS and /WE define the operation to be executed.                                                                                              |

| 18                                                                                                             | /CAS     | (Column Address Strobe)<br>Referred to /RAS                                                                                                                                                                                                  |

| 17                                                                                                             | WE       | (Write Enable)<br>Referred to /RAS                                                                                                                                                                                                           |

# Pin Description (Simplified)

| Pin                         | Name             | Function                                                                                                                                                                                                                |

|-----------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16,71,28,59                 | DQM0~3           | <b>(Input/Output Mask)</b><br>The output buffer is placed at Hi-Z (with latency of 2) when<br>DQM is sampled high in read cycle. In write cycle, sampling<br>DQM high will block the write operation with zero latency. |

| 68                          | CLK              | <b>(Clock Inputs)</b><br>System clock used to sample inputs on the rising edge of clock.                                                                                                                                |

| 67                          | CKE              | <b>(Clock Enable)</b><br>CKE controls the clock activation and deactivation. When CKE<br>is low, Power Down mode, Suspend mode, or Self Refresh<br>mode is entered.                                                     |

| 1,15,29,43                  | Vdd              | <b>(Power)</b><br>Power for input buffers and logic circuit inside DRAM.                                                                                                                                                |

| 44,58,72,86                 | V <sub>SS</sub>  | <b>(Ground)</b><br>Ground for input buffers and logic circuit inside DRAM.                                                                                                                                              |

| 3,9,35,41,49,<br>55,75,81   | VDDQ             | (Power for I/O buffer)<br>Separated power from VDD, to improve DQ noise immunity.                                                                                                                                       |

| 6,12,32,38,<br>46,52,78, 84 | V <sub>SSQ</sub> | (Ground for I/O Buffer)<br>Separated ground from VSS, to improve DQ noise immunity.                                                                                                                                     |

| 14,30,57,<br>69,70,73       | NC               | (No Connection)<br>No connection.                                                                                                                                                                                       |

#### Absolute Maximum Rating

| Symbol                             | Item                        | Ratii              | Units |    |

|------------------------------------|-----------------------------|--------------------|-------|----|

| V <sub>IN</sub> , V <sub>OUT</sub> | Input, Output Voltage       | -1.0 ~ -           | V     |    |

| $V_{DD}, V_{DDQ}$                  | Power Supply Voltage        | -1.0 ~ -           | V     |    |

| T <sub>OPR</sub>                   | Operating Temperature Range | Commercial 0 ~ +70 |       | °C |

| T <sub>STG</sub>                   | Storage Temperature         | -55~+150           |       | °C |

| P <sub>D</sub>                     | Power Dissipation           | 1                  |       | W  |

| I <sub>OUT</sub>                   | Short Circuit Current       | 50                 |       | mA |

*Note:* Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and reliability of the device.

# Capacitance (V<sub>CC</sub>=3.3V, f=1MHz, T<sub>A</sub>=25°C)

| Symbol          | Parameter                                                               | Min. | Max. | Units |

|-----------------|-------------------------------------------------------------------------|------|------|-------|

| Cı              | Input Capacitance (A0 to A11, BS0,BS1, /CS, /RAS, /CAS , /WE, DQM, CKE) | 2    | 4    | pF    |

| C <sub>IO</sub> | Input/Output Capacitance                                                | 4    | 6    | pF    |

*Note:* These parameters are periodically sampled and not 100% tested

#### Recommended DC Operating Conditions ( $T_A$ =-0°C ~+70°C)

| Symbol           | Parameter                             | Min. | Тур. | Max.                 | Units |

|------------------|---------------------------------------|------|------|----------------------|-------|

| V <sub>DD</sub>  | Power Supply Voltage                  | 3.0  | 3.3  | 3.6                  | V     |

| V <sub>DDQ</sub> | Power Supply Voltage (for I/O Buffer) | 3.0  | 3.3  | 3.6                  | V     |

| V <sub>IH</sub>  | Input High Voltage (Note 1)           | 2.0  | -    | V <sub>DD</sub> +0.3 | V     |

| VIL              | Input Low Voltage (Note 2)            | -0.3 | -    | 0.8                  | V     |

**Note 1**: VIH (max.) = VDD/VDDQ+1.5V for pulse width  $\leq$  5 nS. **Note 2**: VIL (min.) = VSS/VSSQ-1.5V for pulse width  $\leq$  5 nS.

# **DC Characteristics**

$(V_{DD}=3.3V\pm0.3V, T_{A}=0^{\circ}C \sim 70^{\circ}C)$

|                    |                                                                                                            |                                                                                                | PC-166MHz |       |  |

|--------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------|-------|--|

| Symbol             | Parameter                                                                                                  | Test Conditions                                                                                | Max.      | Units |  |

| I <sub>DD1</sub>   | Operating Current (One bank activ<br>tRC ≥ tRC(min), Outputs Open, In<br>transition per one cycle          |                                                                                                | 95        |       |  |

| I <sub>DD2N</sub>  | Precharge Standby Current in non<br>tCK = 15ns, CS# ≥ VIH(min), CKE<br>Input signals are changed every 20  | ≥ VIH                                                                                          | 25        |       |  |

| I <sub>DD2NS</sub> | Precharge Standby Current in non tCK = $\infty$ , CLK $\leq$ VIL(max), CKE $\geq$                          |                                                                                                | 15        |       |  |

| I <sub>DD2P</sub>  | Precharge Standby Current in pow<br>tCK = 15ns, CKE ≤ VIL(max)                                             | 2                                                                                              |           |       |  |

| I <sub>DD2PS</sub> | Precharge Standby Current in pow<br>tCK = $\infty$ , CKE $\leq$ VIL(max)                                   | 2                                                                                              |           |       |  |

| I <sub>DD3N</sub>  | Active Standby Current in non-pov<br>tCK = 15ns, CKE ≥ VIH(min), CS#<br>Input signals are changed every 20 | 35                                                                                             | mA        |       |  |

| I <sub>DD3NS</sub> | Active Standby Current in non-pov<br>CKE≥ VIH(min), CLK ≤ VIL(max),                                        | 30                                                                                             |           |       |  |

| I <sub>DD4</sub>   | Operating Current (Burst mode)<br>tCK =tCK(min), Outputs Open, Mu                                          | 100                                                                                            |           |       |  |

| I <sub>DD5</sub>   | Refresh Current<br>tRC ≥ tRC(min)                                                                          | 130                                                                                            |           |       |  |

| I <sub>DD6</sub>   | Self Refresh Current<br>CKE ≤ 0.2V ; for other inputs VIH≧                                                 | Self Refresh Current CKE $\leq$ 0.2V ; for other inputs VIH $\geq$ VDD - 0.2V, VIL $\leq$ 0.2V |           |       |  |

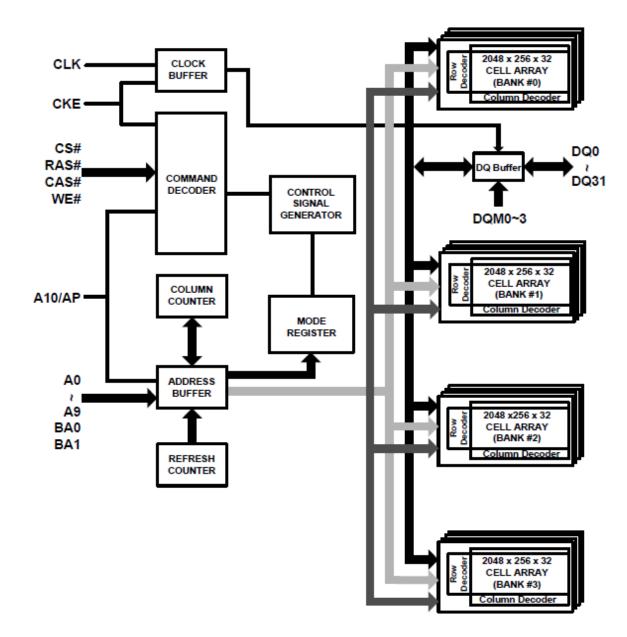

### Block Diagram

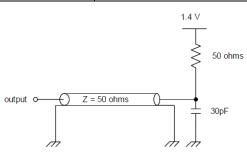

# AC Operating Test Conditions

(V<sub>DD</sub>=3.3V±0.3V, T<sub>A</sub>=0°C ~70°C)

| Item                             | Conditions           |  |  |

|----------------------------------|----------------------|--|--|

| Output Reference Level           | 1.4V/1.4V            |  |  |

| Output Load                      | See diagram as below |  |  |

| Input Signal Level               | 2.4V/0.4V            |  |  |

| Transition Time of Input Signals | 1ns                  |  |  |

| Input Reference Level            | 1.4V                 |  |  |

AC TEST LOAD

### AC Characteristics

(V<sub>DD</sub>=3.3V±0.3V, T<sub>A</sub>=0°C ~70°C)

| Symbol            | Deremeter                                             | 166 I          | MHz  | Units |       |

|-------------------|-------------------------------------------------------|----------------|------|-------|-------|

| Symbol            | Parameter                                             |                | Min. | Max.  | Units |

| $T_{RC}$          | Row cycle time (same bank)                            | 60             | -    | ns    |       |

| T <sub>RCD</sub>  | RAS# to CAS# delay (same bank)                        |                | 18   | -     | ns    |

| $T_{RP}$          | Precharge to refresh/row activate command (same bank) |                | 18   | -     | ns    |

| T <sub>RRD</sub>  | Row activate to row activate delay (different banks)  |                | 12   | -     | ns    |

| T <sub>RAS</sub>  | Row activate to precharge time (same bank)            |                | 42   | 100K  | ns    |

| $T_{WR}$          | Write recovery time                                   |                | 2    | -     | tck   |

| T <sub>CCD</sub>  | CAS# to CAS# Delay time                               | 1.0            | -    | tck   |       |

|                   |                                                       | CL*=2          | -    | 6     | ns    |

| t <sub>CK</sub>   | Clock cycle time                                      | CL*=3          | -    | 5.4   | ns    |

| t <sub>CH</sub>   | Clock high time                                       | 2.5            | -    | ns    |       |

| t <sub>CL</sub>   | Clock low time                                        | Clock low time |      |       | ns    |

| Ŧ                 | Access time from CLK (positive edge)                  | CL*=2          | -    | 6     | ns    |

| $T_{AC}$          | Access time from CLK (positive edge)                  | CL*=3          | -    | 5.4   | ns    |

| Т <sub>он</sub>   | Data output hold time                                 |                | 2.5  | -     | ns    |

| $T_{LZ}$          | Data output low impedance                             |                | 1    | -     | ns    |

| T <sub>HZ</sub>   | Data output high impedance                            | -              | 5.4  | ns    |       |

| T <sub>IS</sub>   | Data/Address/Control Input set-up time                | 1.5            | -    | ns    |       |

| Т <sub>IH</sub>   | Data/Address/Control Input hold time                  | 1              | -    | ns    |       |

| T <sub>PDE</sub>  | Power Down Exit set-up time                           | Tis+tck        | -    | ns    |       |

| T <sub>REFI</sub> | Average Refresh Interval Time                         |                | -    | 15.6  | us    |

# AC Characteristics (Continued)

$(V_{DD}=3.3V\pm0.3V, T_{A}=0^{\circ}C \sim 70^{\circ}C)$

| Symbol           | Parameter                        | 166 N   | Units |       |

|------------------|----------------------------------|---------|-------|-------|

| Symbol           | Faidilleter                      | Min.    | Max.  | Units |

| T <sub>XSR</sub> | Exit Self-Refresh to Any Command | tRC+tIS | -     | ns    |

| T <sub>MRD</sub> | Mode Register Set cycle time     | 2       | -     | tCK   |

| t <sub>RFC</sub> | Refresh cycle time               | 60      | -     | ns    |

\* CL is CAS Latency.

*Note 8:* tHZ defines the time in which the outputs achieve the open circuit condition and are not at reference levels. *Note 9:* If clock rising time is longer than 1 ns, (tR / 2 - 0.5) ns should be added to the parameter.

Note 10: Assumed input rise and fall time tT (tR & tF ) = 1 ns

If tR or tF is longer than 1 ns, transient time compensation should be considered, i.e., [(tr + tf)/2 - 1] ns should be added to the parameter.

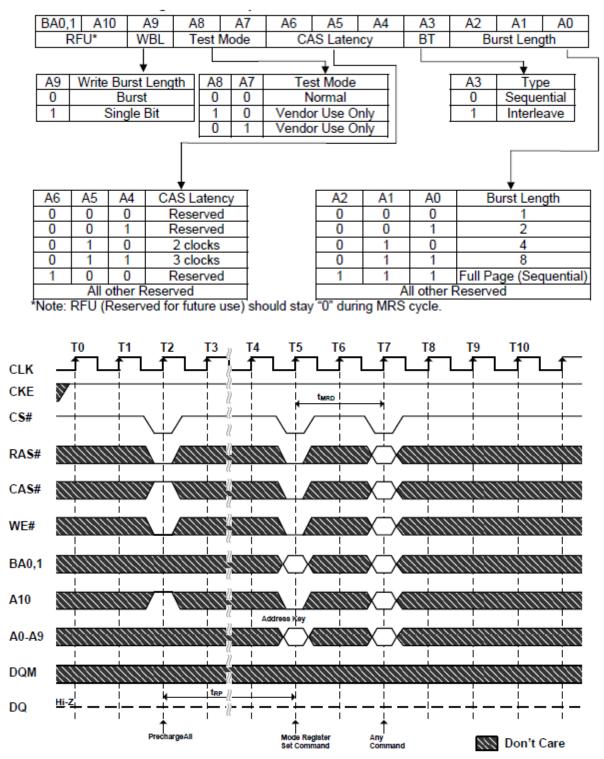

### **Recommended Power On and Initialization**

The following power on and initialization sequence guarantees the device is preconditioned to each user's specific needs. (Like a conventional DRAM) During power on, all  $V_{DD}$  and  $V_{DDQ}$  pins must be built up simultaneously to the specified voltage when the input signals are held in the "NOP" state. The power on voltage must not exceed  $V_{DD}$ +0.3V on any of the input pins or  $V_{DD}$  supplies. (CLK signal started at same time) After power on, an initial pause of 200 µs is required followed by a precharge of all banks using the precharge command.

To prevent data contention on the DQ bus during power on, it is required that the DQM and CKE pins be held high during the initial pause period. Once all banks have been precharged, the Mode Register Set Command must be issued to initialize the Mode Register. A minimum of eight Auto Refresh cycles (CBR) are also required, and these may be done before or after programming the Mode Register.

#### Address Input for Mode Register Set

| Burst Length | A2 | A1 | A0 | Sequential Addressing | Interleave Addressing |

|--------------|----|----|----|-----------------------|-----------------------|

| 2            | Х  | Х  | 0  | 0 1                   | 01                    |

| 2            | Х  | Х  | 1  | 10                    | 10                    |

|              | Х  | 0  | 0  | 0123                  | 0123                  |

| 4            | Х  | 0  | 1  | 1230                  | 1 0 3 2               |

| 4            | Х  | 1  | 0  | 2301                  | 2301                  |

|              | Х  | 1  | 1  | 3012                  | 3210                  |

|              | 0  | 0  | 0  | 01234567              | 01234567              |

|              | 0  | 0  | 1  | 1 2 3 4 5 6 7 0       | 10325476              |

|              | 0  | 1  | 0  | 23456701              | 23016745              |

| 8            | 0  | 1  | 1  | 34567012              | 32107654              |

| 0            | 1  | 0  | 0  | 45670123              | 45670123              |

|              | 1  | 0  | 1  | 56701234              | 54761032              |

|              | 1  | 1  | 0  | 67012345              | 67452301              |

|              | 1  | 1  | 1  | 70123456              | 76543210              |

| Full Page*   | n  | n  | n  | Cn Cn+1 Cn+2          | -                     |

\* Page length is a function of I/O organization and column addressing

32 (CA0 ~ CA7): Full page = 256bits

# Burst Length Field(A2~A0)

| A2 | A1 | A0 | Burst Length |

|----|----|----|--------------|

| 0  | 0  | 0  | 1            |

| 0  | 0  | 1  | 2            |

| 0  | 1  | 0  | 4            |

| 0  | 1  | 1  | 8            |

| 1  | 0  | 0  | Reserved     |

| 1  | 0  | 1  | Reserved     |

| 1  | 1  | 0  | Reserved     |

| 1  | 1  | 1  | Full Page    |

H = High level, L = Low level, X = High or Low level (Don't care), V = Valid data input

# Burst Type Field

| A3 | Burst Type |

|----|------------|

| 0  | Sequential |

| 1  | Interleave |

### CAS Latency Field (A6~A4)

| A6 | A5 | A4 | CAS Latency |

|----|----|----|-------------|

| 0  | 0  | 0  | Reserved    |

| 0  | 0  | 1  | Reserved    |

| 0  | 1  | 0  | 2 Clocks    |

| 0  | 1  | 1  | 3 Clocks    |

| 1  | Х  | Х  | Reserved    |

### Test Mode Field (A8~A7)

| A8 | Α7 | Test Mode       |

|----|----|-----------------|

| 0  | 0  | Normal Mode     |

| 0  | 1  | Vendor Use only |

| 1  | Х  | Vendor Use only |

### Write Burst Length (A9)

| A9 | Write Burst Length      |  |  |  |

|----|-------------------------|--|--|--|

| 0  | Burst-Read-Burst-Write  |  |  |  |

| 1  | Burst-Read-Single-Write |  |  |  |

#### **No-Operation command**

(RAS# = "H", CAS# = "H", WE# = "H")

The No-Operation command is used to perform a NOP to the SDRAM which is selected (CS# is Low). This prevents unwanted commands from being registered during idle or wait states.

#### **Burst Stop command**

(RAS# = "H", CAS# = "H", WE# = "L")

The Burst Stop command is used to terminate either fixed-length or full-page bursts. This command is only effective in a read/write burst without the auto precharge function.

Fully synchronous operations are performed to latch the commands at the positive edges of CLK. Table 4 shows the truth table for the operation commands.

### Truth Table

| Command                  | State                 | CKE <sub>n-1</sub> | CKEn | DQM <sup>(6)</sup> | BA0,1 | A10  | A0-9                 | CS# | RAS# | CAS# | WE# |

|--------------------------|-----------------------|--------------------|------|--------------------|-------|------|----------------------|-----|------|------|-----|

| BankActivate             | Idle <sup>(3)</sup>   | Н                  | Х    | Х                  | V     | Row  | address              | L   | L    | Н    | Н   |

| BankPrecharge            | Any                   | Н                  | Х    | Х                  | V     | L    | Х                    | L   | L    | Η    | L   |

| PrechargeAll             | Any                   | Н                  | Х    | Х                  | Х     | Η    | Х                    | L   | L    | Η    | L   |

| Write                    | Active <sup>(3)</sup> | Н                  | Х    | V                  | V     | L    | Column<br>address    | L   | Н    | L    | L   |

| Write and AutoPrecharge  | Active <sup>(3)</sup> | Н                  | Х    | V                  | V     | Н    | (A0 ~ A7)            | L   | Н    | L    | L   |

| Read                     | Active <sup>(3)</sup> | Н                  | Х    | V                  | V     | L    | Column               | L   | Н    | L    | Н   |

| Read and Autoprecharge   | Active <sup>(3)</sup> | Н                  | Х    | V                  | V     | Н    | address<br>(A0 ~ A7) | L   | Н    | L    | Н   |

| Mode Register Set        | Idle                  | Н                  | Х    | Х                  |       | OP c | ode                  | L   | L    | L    | L   |

| No-Operation             | Any                   | Н                  | Х    | Х                  | Х     | Х    | Х                    | L   | Н    | Н    | Н   |

| Burst Stop               | Active <sup>(4)</sup> | Н                  | Х    | Х                  | Х     | Х    | Х                    | L   | Н    | Н    | L   |

| Device Deselect          | Any                   | Н                  | Х    | Х                  | Х     | Х    | Х                    | н   | Х    | Х    | Х   |

| AutoRefresh              | Idle                  | Н                  | Н    | Х                  | Х     | Х    | Х                    | L   | L    | L    | Н   |

| SelfRefresh Entry        | Idle                  | Н                  | L    | Х                  | Х     | Х    | Х                    | L   | L    | L    | Н   |

| SelfRefresh Exit         | Idle                  | L                  | Н    | Х                  | X     | Х    | х                    | Н   | Х    | Х    | Х   |

|                          | (SelfRefresh)         |                    |      |                    |       |      |                      | L   | Н    | Н    | Н   |

| Clock Suspend Mode Entry | Active                | Н                  | L    | Х                  | Х     | Х    | Х                    | н   | Х    | Х    | Х   |

|                          |                       |                    |      |                    |       |      |                      | L   | V    | V    | V   |

| Power Down Mode Entry    | Any <sup>(5)</sup>    | Н                  | L    | Х                  | X     | Х    | Х                    | н   | Х    | Х    | Х   |

|                          |                       |                    |      |                    |       |      |                      | L   | Н    | Н    | Н   |

| Clock Suspend Mode Exit  | Active                | L                  | Н    | Х                  | Х     | Х    | Х                    | Х   | Х    | Х    | Х   |

| Power Down Mode Exit     | Any                   | L                  | Н    | Х                  | X     | Х    | Х                    | н   | Х    | Х    | Х   |

|                          | (PowerDown)           |                    |      |                    |       |      |                      | L   | Н    | Н    | Н   |

| Data Write/Output Enable | Active                | Н                  | Х    | L                  | Х     | Х    | Х                    | Х   | Х    | Х    | Х   |

| Data Mask/Output Disable | Active                | Н                  | Х    | Н                  | Х     | Х    | Х                    | Х   | Х    | Х    | Х   |

#### Note :

- 1. V = Valid, X = Don't care, L = Logic low, H = Logic high

- 2. CKEn signal is input level when commands are provided.

- CKEn-1 signal is input level one clock cycle before the commands are provided.

- 3. These are states of bank designated by BA signal.

- 4. Device state is 1, 2, 4, 8, and full page burst operation.

- 5. Power Down Mode can not enter in the burst operation.

- When this command is asserted in the burst cycle, device state is clock suspend mode.

- 6. DQM0-3

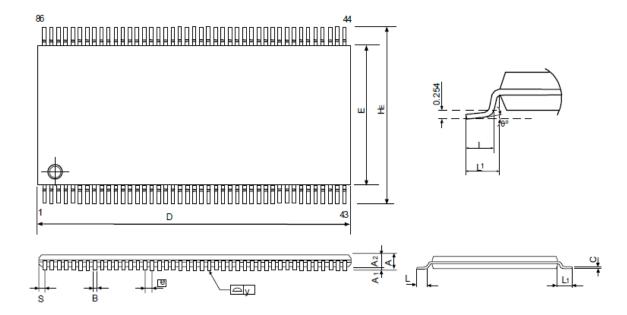

# 86 Pin TSOP II Package Outline Drawing Information

| Symbol | Din   | nension in ir | nch   | Dimension in mm |        |       |  |

|--------|-------|---------------|-------|-----------------|--------|-------|--|

| Symbol | Min   | Normal        | Max   | Min             | Normal | Max   |  |

| Α      | _     | _             | 0.047 | _               | _      | 1.20  |  |

| A1     | 0.002 | 0.004         | 0.008 | 0.05            | 0.10   | 0.2   |  |

| A2     | 0.035 | 0.039         | 0.043 | 0.9             | 1      | 1.1   |  |

| В      | 0.007 | 0.009         | 0.011 | 0.17            | 0.22   | 0.27  |  |

| С      | _     | 0.005         | _     | _               | 0.127  | _     |  |

| D      | 0.87  | 0.875         | 0.88  | 22.09           | 22.22  | 22.35 |  |

| E      | 0.395 | 0.400         | 0.405 | 10.03           | 10.16  | 10.29 |  |

| e      | _     | 0.0197        | —     | _               | 0.50   | _     |  |

| HE     | 0.455 | 0.463         | 0.471 | 11.56           | 11.76  | 11.96 |  |

| L      | 0.016 | 0.020         | 0.024 | 0.40            | 0.50   | 0.60  |  |

| L1     | _     | 0.0315        | _     | _               | 0.80   | _     |  |

| S      | _     | 0.024         | _     | _               | 0.61   | _     |  |

| У      | _     | _             | 0.004 | _               | _      | 0.10  |  |

| θ      | 0°    | _             | 8°    | 0°              | _      | 8°    |  |

#### Notes:

1. Dimension D&E do not include interlead flash.

2. Dimension B does not include dambar protrusion/intrusion.

- 3. Dimension S includes end flash.

- 4. Controlling dimension: mm

# **Revision History**

| Revision No. | History              | Draft Date | Editor    | Remark |

|--------------|----------------------|------------|-----------|--------|

| 0.1          | Initial Release.     | Apr. 2018  | Rico Yang | N/A    |

| 1.0          | First SPEC. release. | Apr. 2018  | Rico Yang | N/A    |